Shane O'Meara, Analog Devices Ltd.

Shane O'Meara, Analog Devices Ltd.

צריכת הספק נמוכה היא דרישת-מפתח עבור יישומי ממירים אנלוגיים-לדיגיטליים (ADCs) של היום המוזנים על-ידי סוללה, כגון מכשירים ידניים-ניידים עבור מגמת שוקי הרפואה, הצריכה והתעשייה לקראת ממדים ומשקל מופחתים, זמני פעולה ארוכים יותר לסוללה (או לטעינת סוללה), ועלות נמוכה יותר, המלווים לעתים קרובות על-ידי מכלול תכונות מוגדל. אין לזלזל ביתרונות של הספק נמוך, אפילו ביישומים לא מוזנים על-ידי סוללות, מאחר שמערכות בעלות הספק נמוך יכולות לפעול ללא גוף קירור או מאווררים, דבר העושה אותן יותר קטנות, יותר זולות, יותר אמינות ויותר "ירוקות". בנוסף, מתכננים רבים עומדים בפני אתגר של תכנון מוצרים בעלי תכונות או ביצועים משופרים, תוך הפחתה, או לפחות לא הגדלה, של תקציבי ההספק הקיימים.

המבחר העצום של ADCs בשוק של היום עושה את בחירתם של החלק הטוב ביותר לשם מילוי דרישות מערכת מיוחדות עוד יותר מאתגרת. מלבד ההערכה הרגילה של מאפייני ביצועי הממירים הרגילים, דוגמת מהירות ודיוק, יש להתחשב בעוד יותר מפרטים כאשר הספק נמוך הוא דרישה מחייבת. הבנה של מפרטים אלה וכיצד החלטות תכנוניות משפיעות על תקציב ההספק חיוניים כדי לקבוע את צריכת ההספק של המערכת ואת חישובי חיי הסוללה.

צריכת ההספק הממוצעת עבור ADC הוא פונקציה של ההספק הנצרך בעת ההמרה, ההספק הנצרך כאשר הוא לא ממיר, וכמות הזמן המושקע בכל מצב. דבר זה ניתן לבטא על-ידי משוואה 1:

PAVG= הספק ממוצע מפוזר

PCONV=הספק מפוזר בזמן ההמרה

PSTBY= הספק מפוזר בזמן מצב – הכן או כיבוי

tCONV= זמן מושקע בהמרה

tSTBY= זמן מושקע במצב-הכן או כיבוי

ההספק המשמש בשעת ההמרה הוא לרוב הרבה יותר גדול מאשר ההספק במצב-הכן, כך שניתן להקטין משמעותית את ההספק הממוצע אם מאריכים את משך המצב-הכן. סוגי הממירים בעלי קירוב רציף (successive approximation – SAR) הם נוחים במיוחד לסוגי פעולה אלה.

אחד הגורמים החשובים ביותר המשפיעים על השימוש בהספק המערכת הוא הבחירה של ספקי-כוח ניידים (on-board). עבור יישומים ניידים, המערכת תוזן לעתים קרובות על-ידי תא מטבע-ליתיום של 3 וולט. דבר זה מונע את הצורך בווסת מתח dropout נמוך, וחוסך בכך בהספק, במקום ובעלות. יישומים ללא-סוללה נהנים גם מממירים בעלי תחומי הזנת VDD נמוכים, מאחר שצריכת ההספק נעה עם מתח המבוא. בחירה של ה-VDD הנמוך ביותר האפשרי עבור ה-ADC תגרום לצריכת הספק נמוכה יותר.

לכל ה-ADCs המיועדים ליישומי הספק נמוך יש מצבי כיבוי או הכן כדי לשמור על האנרגיה בזמן חוסר הפעילות. ה-ADC ניתן לכיבוי בין המרות יחידות, או שניתן לבצע שורת המרות בקצב תפוקה גבוה, כאשר ה-ADC הוא כבוי בין המרות אלה. לגבי ממירים בעלי ערוץ יחיד, הבקרה של אופני הפעולה יכולה להשתלב בתוך ממשק התקשורת או יכולה לפעול אוטומטית לאחר שההמרה הושלמה.

היתרון של שילוב בקרת המצב בתוך ממשק התקשורת הוא בהפחתת מספר הפינים. דבר זה גורם לצריכת הספק נמוכה יותר, מאחר שיש להזין פחות מבואות ופחות זרמי זליגה. מספר פינים קטן יותר גורם גם לממדי מארז קטנים יותר וכמו כן פחות I/O דרוש על-ידי ה-MCU. ללא תלות בשיטת הבקרה, שימוש זהיר בשיטות אלו יגרום לחסכונות משמעותיים בהספק.

ההספק מוקטן במצבי כיבוי, כפי שהשם מרמז, על-ידי כיבוי חלק ממעגלי ה-ADC. הזמן הדרוש למעגלים הכבויים לחדש את ההמרה קובע את קצב התפוקה בו ניתן להשתמש בשיטות אלו. עבור ADC בעל ייחוס פנימי, זמן ההתחלה המחודשת ייקבע על-ידי הזמן הדרוש לשם טעינה מחדש של קבל הייחוס. ממירים אנלוגיים-לדיגיטליים המשתמשים בייחוס חיצוני דורשים זמן מספיק כדי לעקוב נכון אחר המבוא האנלוגי בזמן ההתחלה מחדש.

לגבי ה-ADCs הנמצאים כיום בשוק, ההספק משתנה לפי התפוקה. ההספק הנצרך הוא שילוב של הספק סטטי ודינמי. ההספק הסטטי הוא קבוע, בשעה שההספק הדינמי משתנה ליניארית עם התפוקה. לכן בחירה של קצב התפוקה הנמוך ביותר האפשרי לשם ביצוע המשימה תגרום לחסכונות בהספק.

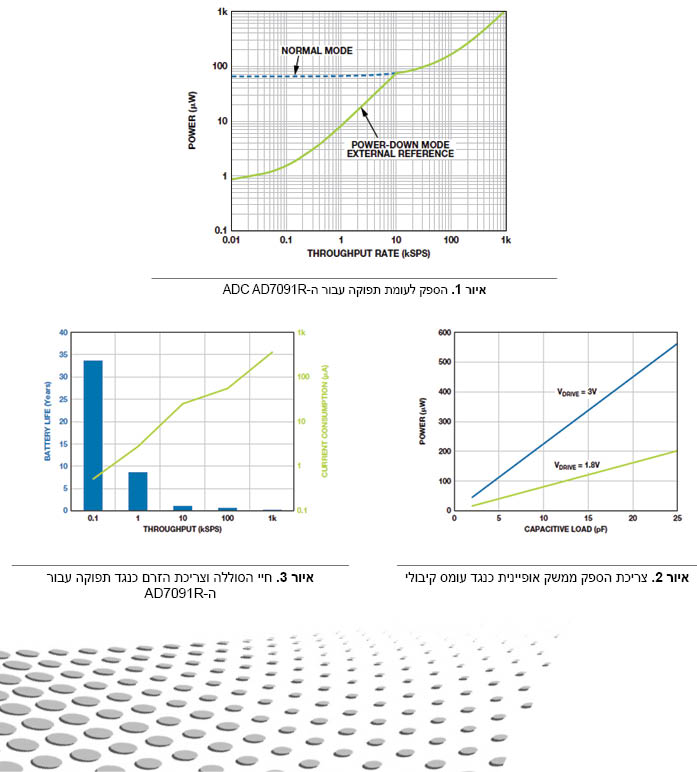

איור 1 מראה את צריכת ההספק

האופיינית עבור ה-AD7091R, ה-ADC החדש בעל ההספק הנמוך ביותר של Analog Devices, כפונקציה של קצב התפוקה. הוא גם מציג השוואה של כיצד השימוש במצב הכיבוי של ההתקן יכול לספק חסכונות נוספים בהספק, במיוחד בקצבי תפוקה נמוכים יותר. קצב התפוקה והשימוש במצב הכיבוי של ה-AD7091R נקבעים על-ידי זמן ההתחלה מחדש של ההתקן, מאחר של-AD7091R יש ייחוס על-השבב, שהוא זמן הטעינה מחדש של קבל הייחוס. הזמן הדרוש לטעון מחדש את קבל הייחוס תלוי בקיבול וברמת המטען שנשאר בקבל כאשר מתחילים מחדש את הייחוס על-השבב.

השיטות המקובלות ביותר ליזום דרישות להמרה ב-ADCs הן פין מבוא להמרה מיוחדת או בקרה דרך הממשק הטורי. עם פין מבוא מיוחד (CONVST), ההמרה יזומה על-ידי קצה נופל (falling edge). ההמרה מבוקרת לאחר מכן על-ידי מתנד על-שבב והתוצאה ניתנת לקריאה חוזרת דרך הממשק הטורי לאחר שההמרה הושלמה. לכן, ההמרה מתנהלת תמיד במהירות מיוטבת קבועה, המאפשרת להתקן להיכנס למצב הספק נמוך ברגע שההמרה היא שלמה, ולחסוך בכך הספק.

עם ADCs בהם הדגימה יזומה על-ידי קצה נופל על בחירת השבב

(chip select – CS), ההמרה מבוקרת על-ידי אות שעון הדגימה הפנימי (sampling clock – SCLK). תדר ה-SCLK ישפיע על זמן ההמרה וקצב התפוקה הניתן להשגה – ולכן, על צריכת ההספק. ככל שקצב ה-SCLK מהיר יותר, זמן ההמרה יהיה קצר יותר. עם זמן המרה קצר יותר, היחס של זמן הזמין עבור ההתקן להיות במצב של הספק נמוך עולה ביחס למצב הרגיל; לכן ניתן להשיג חיסכון משמעותי בהספק. כלומר, אם כל המרה דורשת N מחזורים של ה-SCLK, אזי עבור S המרות לשנייה, הזמן הכולל שה-SCLK מתמתג הוא SXN/fSCLK, והזמן השקט בשנייה מוצג במשוואה 2:

לכן, עבור מספר נתון של דגימות בשנייה, ככל שה-fSCLK עולה, כך עולה גם הזמן השקט בשנייה.

לדוגמה, בהנחה שדרושים 16 SCLK מחזורים כדי להשלים המרה ולקרוא את התוצאות, מערכת הדוגמת ב-100 kSPS עם SCLK של 30 מגה-הרץ תהיה שקטה 94.67% מהזמן, כלומר, היא תידרש ל-5.33% מהזמן לשם המרה (53.3 מילישניות לשנייה). אותה המערכת הפועלת עם SCLK של 10 מגה-הרץ תהיה שקטה רק 84% מהזמן, כלומר, היא תימצא 160 מילי-שניות בהמרה. לכן, כדי להשיג את צריכת ההספק המיטבית, יש להפעיל את הממיר בתדר ה-SCLK הגבוה ביותר האפשרי.

פרמטר חשוב אך מוזנח לעתים קרובות כאשר מתכננים עבור הספק נמוך הוא העומס הקיבולי הנראה בפיני המוצא, במיוחד פיני ממשק התקשורת, כגון

SCLK ,CS ו-SDO, מאחר שמשתני I/O אלה משנים בקביעות את המצב במהלך תהליך ההמרה. העומס הקיבולי שנראה במוצא הוא קיבול הפין של המזין IC בעצמו, ועוד קיבול הפין של פין המבוא, ועוד קיבול העקיבה של המעגל המודפס. ניתן לשמור לרוב על קיבול עקיבה קטן, בתחום ה-femtofarad, והוא איננו משמעותי. ההספק הדרוש כדי לטעון עומס קיבולי (PL) הוא פונקציה של העומס (CL), מתח ההזנה (VDRIVE) ותדר השינוי (f), כמוגדר במשואה 3:

ההספק עבור מערכת שלימה הוא, לכן, סכום המכפלות של קיבול העומס (CLn) כפול תדר המיתוג (fn) כפול ריבוע מתח ההזנה.

בשעה שה-ADC מזין את פין ה-SDO, והמיקרו-בקר המארח מזין את פיני ה-CS, CONVST ו-SCLK, צריכת ההספק הנמוכה ביותר תושג על-ידי מזעור קיבול הפין עבור כל ההתקנים.

לגבי הפינים CS ו-CONVST, תדר המיתוג נקבע רק על-ידי קצב התפוקה. יש לקבוע את תדר ה-SCLK, כפי שנדון קודם לכן, לתדר המותר המרבי כדי להקטין את ההספק. זו איננה סתירה: הנקודה החשובה היא

שה-SCLK איננו רץ חופשי – הוא אמור להיות פעיל רק עבור הזמן המזערי האפשרי כדי לשדר את התוצאה על קו ה-SDO עבור כל ניסוי ביטים ולבקר את תהליך ההמרה. דבר זה תלוי בהתקן וברזולוציה אך הוא לרוב מחזור אחד לביט, בתוספת תקורה מסוימת, או כ-16 SCLK מחזורים לדגימה עבור ממשקי SPI של ממיר 12-ביט. התדר המזערי עבור ה-SCLK הוא, לכן, מספר המחזורים הדרוש כפול קצב התפוקה.

התדר של קו ה-SDO תלוי הן בקצב התפוקה והן בתוצאת ההמרה. משום שדבר זה איננו ניתן לבקרה, המתכננים צריכים להבין כיצד הוא עשוי להשפיע על צריכת ההספק עבור המרה. צריכת ההספק הגבוהה ביותר תהיה כאשר התוצאה היא רצף 101010…; הנמוכה ביותר תהיה כאשר התוצאה היא כולה אחדים או כולה אפסים.

מלבד קצב התפוקה הנמוך יותר, מתח VDRIVE מופחת יצמצם משמעותית את צריכת ההספק. לממירים אנלוגיים לדיגיטליים יש או פין הספקה-יחיד או הספקות נפרדות עבור המעגלים האנלוגיים והממשק הדיגיטלי. הספקה של VDRIVE נפרדת מקנה יותר גמישות תכנונית ומונעת את הצורך במשני-רמה (level shifters), מאחר שניתן לתאם את מתח הממשק האנלוגי-לדיגיטלי לזה של ה-SPI master. בחירה של המתח הנמוך ביותר האפשרי עבור VDRIVE תתאים לצריכת ההספק הנמוכה ביותר במערכת.

איור 2 משווה את דרישת ההספק האופיינית של ממשק SPU תקני – עם CS, SDO ו-SCLK – כפונקציה של העומס הקיבולי הכולל עבור ערכי VDRIVE של 3 וולט ו-1.8 וולט, קצב תפוקה של

100kSPS, מחזורי SCLK להמרה, ומוצא SDO הגרוע ביותר של 1010… עבור ADC בעל 12ביט.

מרכיבים אופייניים אחרים של תכנון מעגל ADC הם ייחוס המתח ומגבר הפרשי. מובן מאליו שיש לבחור גם מרכיבים אלה להספק נמוך. ניתן להשיג ייחוסים אחדים בעלי מצבי הספק נמוך כדי להפחית את הצריכה במשך תקופות חוסר פעילות. בחירת המגבר היא תלויה ביישום, כך שיש להתחשב בקצב התפוקה של המערכת כדי להבטיח שהמגבר שנבחר ממרב את ביצועי ה-ADC וממזער את צריכת ההספק.

ה-AD7091R בעל 12ביט, המתוכנן במיוחד עבור יישומים של הספק נמוך, מכיל ממשק SPI, ייחוס מתח של 2.5 וולט וקצב דגימה של 1-MSPS. ההמרות יזומות דרך פין CONVST. מתנד על-שבב מבקר את תהליך ההמרה, ומאפשר לייטב את צריכת ההספק. קיבול הפין הוא נמוך עד כדי 5pF מרבי. תחום מתחי מבוא רחב (2.7 וולט עד 5.25 וולט) מאפשר שילוב בתחום רחב יותר של יישומים מאשר אלה המוזנים רק על-ידי סוללה. מקור VDRIVE נפרד של 1.65 וולט עד 5.25 וולט מאפשר הספק מופחת ויכולות שילוב במערכת גדולות יותר.

כאשר מופעל ב-1MSPS, ה-AD7091R צורך 349 מיקרו-אמפר טיפוסי ב-VDD של 3 וולט. מאחר שההספק משתנה עם התפוקה, ניתן להשיג זרם שקט של 55 מיקרו-אמפר ב-100kSPS. הזרם הסטטי, כאשר אין המרה, אולם עם הייחוס פעיל, הוא 21.6 מיקרו-אמפר; במצב הספק-נמוך, הצריכה היא רק 264 ננו-אמפר. ה-AD7091R זמין במארזים

MSOP- מוליכים ו-LFCSP.

מגברים אופייניים כדי להזין את ה-AD7091R יכללו את ה-AD8031 – עבור יישומי תפוקה מהירה – ו-AD8420 עבור יישומים בעלי רוחב-פס נמוך יותר. צריכת הזרם השקט האופיינית של ה-AD8031 היא 750 מיקרו-אמפר עם הזנה של 2.7 וולט; זו של ה-AD8420 היא 70 מיקרו-אמפר אופיינית בשימוש עם ספק של 5 וולט.

איור 3 מראה צריכת זרם אופיינית וחיי סוללה מחושבים עבור ה-AD7091R המוזן על-ידי סוללת ליתיום CR2032. אפשר לראות בבירור שכאשר התפוקה יורדת, ניתן להאריך משמעותית את חיי הסוללה.

כאשר משווים את ה-AD7091R עם רוב ה-ADCs האחרים, ניתן להשיג חסכונות משמעותיים בתקציב ההספק. לדוגמה, כאשר משווים נגד המתחרה הקרוב ביותר הקיים, חלק ללא ייחוס פנימי, עבור קצב תפוקה של 1-MSPS, ה-AD7091R משיג יותר מפי שלושה הפחתה בצריכת ההספק (1 מילי-ואט בהשוואה ל-3.9 מילי-ואט עבור הזנה של 3 וולט). דבר זה מתאים להארכה של חיי הסוללה של CR-2032 ב-400 שעות. כאשר לוקחים בחשבון את הצורך לייחוס מתח חיצוני של התקן אחר, החסכונות מוגדלים עוד יותר.

סיכום

קיימים יתרונות רבים של הפחתת צריכת ההספק מלבד הארכה של חיי הסוללה. מופק פחות חום, דבר הגורם לגורמי צורה קטנים יותר. האמינות משתפרת, בשל המאמץ הנמוך יותר של טמפרטורה. ניתן להפחית את עלויות המערכת, מאחר שניתן להקטין את ממדי המעגל המודפס בשל הרכיבים הקטנים יותר – עם הפחתה במספר הרכיבים, מאחר שאין צורך באביזרים דוגמת גוף קירור.

מאמר זה הדגיש מספר שיקולים ויתרונות חשובים שמתכנן המערכת צריך להביא בחשבון בקשר לייטוב של צריכת ההספק בתכנונים שלו הכוללים ADCs.

סימוכין

Casamayor, Mercedes and Claire Croke. “How to Save Power in Battery Applications Using the Power-Down Mode in an ADC.” Analog Dialogue, Vol. 37, No. 3, pp. 3-9, 2003

אודות המחבר

Shane O'Meara הוא מהנדס יישומים ב-Analog Devices. הוא הצטרף ל-ADI ב-2011 ועובד בקבוצת יישומי ממירים מדויקים ב-Limerick, אירלנד. הוא קיבל תואר BEng בהנדסת אלקטרוניקה מהאוניברסיטה של Limerick.