מאת: Haim Cohen, Freescale Semiconductors

מאת: Haim Cohen, Freescale Semiconductors

מבוא: באוויוניקה, בהגנה ובתעבורה, בדומה לכל תחומי העיבוד המתקדמים ביותר, מחפשים דרכים לשפר ביצועים ובו בזמן לצמצם את תקציבי צריכת החשמל וגורם הצורה הקיימים.

אם השימוש במערכות על שבב מרובות ליבות של COTS יהפוך לגישה השכיחה לעמידה ביעדי התכנון כיום, הרי ששילובן במערכות משובצות מעלה מספר פרדיגמות חדשות כששוקלים יעדי מפתח הקשורים לאבטחה ולאישור.

מאמר זה מתמצת ומדגיש את מאפייניהם הספציפיים של מעבדים מרובי ליבות כדוגמת Freescale QorIQ 45nm (מסדרת P P4080 על נגזרותיה) ו-28nm החדש (מסדרת T T4240 על נגזרותיה) תוך התמקדות ביישומי אבטחה באוויוניקה, הגנה ותעבורה.

חלוקה קשיחה מתווה מערכת מנגנונים הנדרשת למיזוג והפרדה של מספר אפליקציות נפרדות במערכת על שבב.

עיבוד וקטורי (כפי שמספקת יחידת Altivec SIMD) עשוי להגביר מהירות במגוון רחב של עיבוד מדעי, עיבוד הדמיה ועיבוד אותות הנדרשים בעיבוד מערכות משובצות מתקדמות.

ניהול הספק מסייע בייעול החלוקה בהתאם לשימוש הממשי במערכת על שבב, בהתחשב במה שמשתמשים ובמה שלא משתמשים בהתנהגות הדינמית ובהתנהגות הסטאטית.

ניפוי באגים וניטור תשתית מסייעים במיזוג HW/SW ושלבי הבדיקה ועשויים להקל על משימות האימות הנדרשות עד לאישור.

מאפייני אבטחה והרשאה עשויים לחזק את שלמות המערכת במובן של הגנה על פרוטוקולי אינטרנט פנימיים חשובים והגנה כנגד ניסיונות פגיעה חיצוניים שנעשו בזדון.

ולבסוף, קבוצת העבודה MCFA (ריבוי ליבות עבור אוויוניקה) נמצאת כאן כדי לסייע למפתחים ציוד ולמתאמים סופיים באוויוניקה אזרחית להשתמש בטכנולוגיה מרובת ליבות ולעסוק בדרישות ספציפיות של אבטחה ואישור.

ארכיטקטורה כללית

המעבדים QorIQ מסדרה P וסדרה T משלבים 1 עד 12 ליבות פיזיות ועד 24 ליבות לוגיות (המכונות "hardware threads") הפועלות במהירות של עד 2 ג'יגה-הרץ ומתבססות על שלושה סוגים שונים של ליבות Power® Architecture:

e500mc 32-bit — single-threaded

e5500 32/64-bit — single-threaded

e6500 32/64-bit — dual-threaded עם

יחידה וקטורית

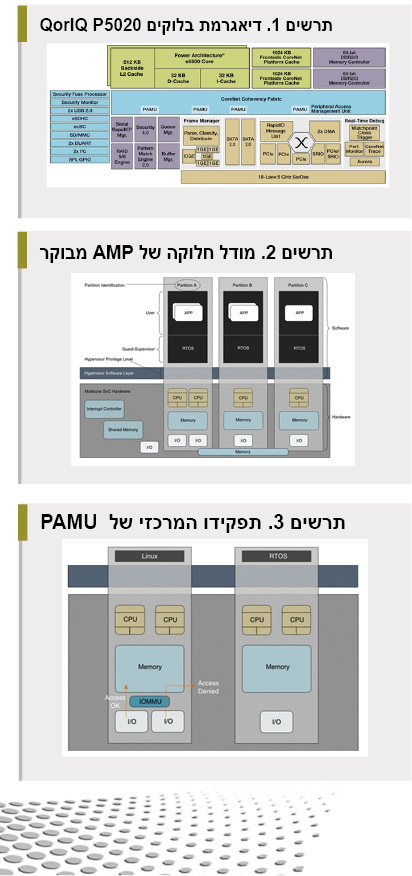

כדוגמה לעקרונות ארכיטקטורה כוללת, תרשים 1 מציג דיאגרמת בלוקים של מערכת על שבב בעלת שתי ליבות P5020.

לכל ליבה יש זיכרון מטמון פרטי L1 להוראות ונתונים. זיכרון מטמון L2 קיים בכל ליבה בכל נגזרות סדרת P ובבני משפחת T1 בסדרה T. L2 קיים בכל אשכול בסדרות T2 ו-T4 המשתמשות בליבת e6500.

בכל המקרים, ניתן להשיג גישה לזיכרונות מטמון L1 ו-L2 מהליבות היחסיות שלהם דרך ממשק ישיר ללא צורך במעבר דרך חיבור מערכת על שבב גלובלי.

נוסף על זמן אחזור הנמוך של זיכרונות מטמון L1 ו-L2 המערכת על שבב מספקת מקור SRAM משותף שבו ניתן להשתמש כזיכרון מטמון L3 הממוקם באפיק קדמי (המכונה גם Corenet Platform Cache -) או כ-SRAM פנימי בעל כתובת קבועה לשם ייעול הגישה לנתונים או לשם הסתרת נתונים פנימיים "סודיים".

כל מיקומי הזיכרון הפנימיים הללו מוגנים מטעות באמצעות סיבית (L1) או ECC (תיקון טעות אחת או תיקון טעות כפולה), דבר הכרחי ליישומי אבטחה.

הקישור ההדדי הפנימי בין מודולי הליבה לבין בלוקי IP של המערכת על שבב האחרים, לרבות SRAM משותף, זיכרון מערכת מסוג DDR, יחידות ציוד היקפי ומאיצי חומרה, מבוצע ברמה הפיזית באמצעות תבנית עקבית בשם ®CoreNet.

CoreNet היא טכנולוגיה של תבנית מיתוג ברוחב פס גבוה המאפשרת למספר פעולות שמתרחשות בו זמנית לזרום במקביל בין מגוון גורמי ומטרות חומרה בתוך מערכת העל שבב.

כל ליבה (בסדרות P ו-1T) או אשכול (בסדרות 4T ו-2T) מחוברת לתבנית CoreNet באמצעות חיבור נקודה-לנקודה עצמאי, שבניגוד לארכיטקטורתbus במערכת הקודמת, מאפשרת להזין במקביל מספר ליבות בנתונים המגיעים מזיכרון פנימי או חיצוני.

חלוקה קשיחה

חלוקה הופכת לדרישה שכיחה במספר תחומי יישום.

בתחומי מערכות משובצות מתקדמות בזמן אמת, כדוגמת אוויוניקה ותעבורה, מתייחסים לכך לעתים כ"חלוקה קשיחה" כדי לתאר את רמות ההפרדה וההגנה הגבוהות המתבקשות בין חלקים שונים בגישת קונפיגורציה סטאטית תוך שימוש בווירטואליזציה נמוכה באופן יחסי (כשבקצה האחר, במתחמים של מרכזי נתונים וצמתי רשת, החלוקה צריכה להיות מיושמת באופן דינמי יותר תוך שימוש בווירטואליזציה מורחבת כדי לחלוק במשאבים פיזיים בסיסיים).

יישום החלוקה במערכת המבוססת על ארכיטקטורת QorIQ מרובת ליבות של Freescale קשורה למספר מאפיינים שונים שפרושים על בלוקי האיי-פי השונים של מערכת העל שבב: ליבות, MMU, זיכרונות מטמון, מבנה קישור הדדי, בקר פסיקה, ציוד היקפי/DMAs וכו'.

בטרמינולוגיה של QorIQ "חלוקה" התייחסה במקור למקבץ הלוגי של משאבי החומרה, כדוגמת CPU/ליבות, חלקים מהזיכרון, I/Os ומאיצים, כתמיכה לדרישות יישום שונות.

ניתן להשתמש בכל משאב באופן פרטי (באמצעות חלוקה אחת) או באופן שיתופי (באמצעות מספר חלוקות).

השימוש השכיח ביותר לחלוקת משאבי חומרה הוא מיזוג של מספר סביבות תוכנה עצמאיות, שיושמו בעבר בתת-מערכות חומרה שונות.

כל חלוקה (כלומר, מערכת של משאבי חומרה) מארחת באופן טיפוסי סביבת תוכנה המורכבת ממערכת הפעלה ומהיישומים שלה. לאור סיבה זו, חלוקה שמתרחבת לסביבת תוכנה זו, הופכת את החלוקה לשילוב של משאבי חומרה ותוכנה.

מודל תוכנה עם מספר מערכות הפעלה הפועלות בו זמנית מכונה "עיבוד מרובב אסימטרי" (AMP), בניגוד ל"עיבוד מרובב סימטרי" (SMP), שבו מערכת הפעלה אחת מנהלת את כל המשאבים.

ארכיטקטורת QorIQ מספקת תמיכה למספר מודלים של חלוקה בהתחשב באופן שבו מספר סביבות SW זקוקות להפרדה.

במודל שיתופי כל החלוקות מנוהלות באותה רמה של הרשאה. במודל זה נדרשות שתי רמות מיוחסות בלבד וזה המודל המסורתי של משתמש/מנהל.

במודל AMP מבוקר (תרשים 2) קיימות מספר מערכות הפעלה עם רמות הרשאה שונות שחייבות להתקיים זו לצד זו.

במקרה זה, החלוקות בעלות ההרשאה הנמוכה חייבות להיות מבוקרות כדי שלא לחרוג בשימוש במשאבים המוקצים בקפדנות לחלקים אלה.

כדי ליישם רמה זו של הגנה, מתווספת רמת הרשאה שלישית המכונה hypervisor.

השימוש ברמת ההרשאה השלישית מייצר שכבת hypervisor SW שפועלת בכל ליבה ואחראית לפקח על כל מערכת הפעלה "אורחת", כך שמערכות הפעלה אלה לא יפרו את תנאי ההרשאה של חלוקת HW שלהן.

לאור זאת, יש להתייחס אל שכבת hypervisor SW כאל מבקרת שגיאות וווירטואליזציית משאבים של המערכת המחולקת.

מעבר לשני המודלים (AMP שיתופי ומבוקר), קיימת אפשרות למספר גרסאות שונות, למשל, שאחת ממערכות ההפעלה תתפקד כ-hypervisor (או וירטואלייזר) עבור מערכות הפעלה אורחות.

חלוקה קשיחה נתמכת בעיקר ע"י שלושה מנגנוני חומרה עיקריים בתוך המערכת על שבב:

יחידת ניהול זיכרון (MMU) לכל ליבה

יחידת ניהול גישה היקפית (PAMU) ברמת החיבור ההדדי

משתמש/מנהל/hypervisor (מודל היררכי בעל שלוש רמות)

MMU הוא מנגנון החומרה ששולט בכל הגישות מבוססות הכתובת שנוצרו ע"י הליבות.

PAMU (תרשים 3) הוא מנגנון דומה ששולט בכל הגישות מבוססות הכתובת שנוצרו ע"י ציוד היקפי התומך ב-DMA.

MMU ו-PAMU הם שני מאפייני האבטחה העיקריים של מערכת מחולקת.

נוסף על שלושת מנגנוני המפתח המוזכרים לעיל, ניתן להוסיף הרחבות רבות ל- QorIQ מסדרות P ו-T על מנת לנהל ביעילות את ההיבטים השונים של חלוקה העוסקת ב:

הגנה ואישור

קוהרנטיות של היררכיית זיכרון

וירטואליזציה של מערכות הפעלה אורחות ניהול פסיקה

תקשורת וסנכרון של ליבה פנימית וחלוקה פנימית

ביישום קריטי בזמן אמת, חלוקה קשיחה עשויה לכלול היבטים מרחביים וזמניים.

חלוקה על בסיס זמן מאתגרת יותר בהקשר של מערכת על שבב מרובת ליבות בשל האינטראקציה הפיזית הרבה המתרחשת בתוך מערכת העל שבב.

כדי לכפות דטרמיניסטיות, עשויים מתכנני המערכת להתחשב במספר אפשרויות כשהם יוצרים חומרה ארכיטקטונית ומקבלים החלטות תוכנה, לרבות:

הפעלה מחדש של מנגנונים אופציונאליים לשיפור ביצועים, כדוגמת זיכרון מטמון שיתופי והשימוש בו במקום ב- RAM רגיל.

הגבלת קוהרנטיות של חומרה כדי לצמצם תקורה של מעבר נתונים.

הגבלת האינטראקציות בין חלוקות ע"י יישום של אסטרטגיות ניהול זמן ב-RTOS או ברמת ה-hypervisor (מערכת תזמון/פריסה).

עיבוד וקטורי

תעשיות התעופה-חלל וההגנה מצריכות ביצוע SIMD (פקודה בודדת על גבי ריבוי נתונים) בתוך תקציבי צריכת החשמל למערכות משובצות.

הן זקוקות לעיבוד אות מהיר, הדמיה בזמן אמת ואלגוריתמים אחרים.

QorIQ מסדרת T, משפחות 4T ו-2T מציגים מחדש את טכנולוגיית העיבוד הווקטורי AltiVec שתוכננה במקור בליבת e600 בארכיטקטורת Power Architecture core.

הדמיית מכ"ם, תצוגות בתא הטייס והרכשת מטרות עשויות לנצל לתועלתן יכולת זו.

AltiVec מרחיב את יחידת השלמים ואת יחידת הנקודה הצפה של e6500 באמצעות יחידת SIMD שמספקת 156 פקודות וקטוריות ופועלת במערכת של אוגרי וקטור משלה ברוחב b128, ומספקת פונקציונליות בדומה למעבדי אותות ספרתיים (DSP) וליחידות עיבוד גרפיות (GPU) באופן מסונכרן.

סוגי הנתונים הנתמכים הם בוליאן, מספרים שלמים ונקודה צפה.

ניתן לבצע עד שתי פקודות SIMD Altivec בכל מחזור, כשכל פקודה יכולה לעבד וקטורים של עד 16 נתונים. בנקודה צפה ברמת דיוק יחיד Altivec מסוגלת לספק ביצועים של עד 192 GFLOPS (פעולות בנקודה צפה בשנייה).

מתכנתים יכולים ליישם את Altivec באמצעות כתיבה מלאה וייעול ספריית הווקטורים שלהם או באמצעות יצירת יישום משלהם על בסיס ספרייה קיימת שתסופק באקו-סיסטם של משפחת סדרה T. ספרייה זו כוללת את כל הפקודות המתמטיות הבסיסיות והסטנדרטיות, הפקודות המדעיות, הפקודות לעיבוד אותות ספרתיים והפקודות הגרפיות.

ניהול צריכת הספק

צריכת הספק היא נושא מפתח ביישומים משובצים, ומעבר לטכניקות שכיחות כדוגמת יצירת שער באמצעות שעון, מצבי הדממת בלוקים שאינם בשימוש או הרדמתם, ניתן להשיג תועלת מסוימת על ידי תזמון כל ליבה (או אשכול במקרה של סדרה T) באופן עצמאי בתדר שמכוון לציפיות הביצועים בפועל מאותה ליבה. שיטה זו משתמשת בניצול ליבות א-סימטרי.

ייתכן גם שיהיה אפשר להתאים באופן דינמי את תדר הליבות במהלך ההפעלה, לשקול תקופות משתנות של פעילויות, ויש לשלוט בכך באמצעות SW. (התאמה לתדר לא דטרמיניסטי כפי שקיימת ביישומי שרת אינה נתמכת).

בסדרת T האחרונה, Freescale הרחיבה את ניהול צריכת ההספק כשאפשרה באמצעות שעון ויצירת שער חשמלי להפחית את חלוקת ההספק לבלוקים פנימיים אלה (ליבה, Altivec, זיכרון מטמון 2L). בעקבות זאת לא נצפתה פעילות במהלך פרק זמן משמעותי.

הדבר היפה הוא שהמצבים הפנימיים של בלוק האיי-פי נשמרים וניתן להפעיל את אותו בלוק מחדש בזמן אחזור די מהיר. באופן זה ניתן לצמצם הן את הרכיבים הקבועים והן את הרכיבים הדינמיים של חלוקת החשמל למצע הסיליקון.

ניפוי באגים וניטור

בשל המורכבות הכוללת של מערכות על שבב מרובות ליבות ולאור העובדה שדטרמיניזם הוא קריטריון מפתח של יישום משובץ מאושר, מעבד מרובה ליבות חייב לספק תמיכה מורחבת לניטור וניפוי באגים של הפעילות והאינטראקציות הפנימיות במערכת על שבב. הדבר היווה שיפור משמעותי בהשוואה לדורות הקודמים בתכנון QorIQ מסדרות P ו-T. לשם מטרה זו שולבה תשתית מושלמת הכוללת נקודות עצירה, מונה אירועים מרובים ומערכת מעקב אחר פעילות בבאפרים.

מאפייני

אבטחה/הרשאה

היבט "האבטחה" כאן קשור להגנה על הציוד עצמו מפני איום פוטנציאלי של כשל תפקודי, סירוב להעניק שירות או הגנה על קניין רוחני פנימי, למשל, מניעה מיישות בלתי צפויה לשכפל ולהשתמש מחדש בקוד חיוני או בחלקי נתונים בציוד.

הדבר מתייחס גם ל"מערכת מאובטחת" כמערכת שעושה מה שיצרני ציוד מקורי (OEM) ומשתמשים מצפים ממנה לעשות ולא עושה מה שיצרני הציוד המקורי והמשתמשים מתייחסים אליו כפעולה הטומנת בחובה נזק.

עד כה, הגנה מעין זו היוותה מקור לחשש ביישומי צרכן ובתחומים משובצים חיוניים מאוד.

בעקבות השימוש במעבדים מרובי ליבות, רמת הגנה זו תיחשב יותר ויותר כשילוב של יישומים עצמאיים רבים ותוביל למספר שחקנים (יצרנים וספקים שונים) שיתקשרו על אותה פלטפורמת חומרה, שלכל אחד תיוחס רמה משתנה של "הרשאה".

Freescale העניקה תשומת לב רבה לדרישות אבטחה אלה ושילבה מנגנונים רבים ב-QorIQ מסדרות P ו-T, לרבות:

אתחול מאובטח

אימות תקופתי מחדש לקוד ולחלקים חיוניים של נתונים באמצעות אישור.

קידוד/הסרת צופן אוטומטיים של סודות חיצוניים

איתור פגיעה בזדון

סיווג ממשקים לניפוי באגים

אם QorIQ יוגדר לבצע אתחול מאובטח, באיפוס ההתקן, ליבה 0 תתפנה לאתחל ביצוע מ-bootROM פנימי הכולל קוד פנימי לאתחול מאובטח (ISBC), שהוא קוד שלא ניתן לשינוי.

ההוראות שמבוצעות מקוד ה-ISBC מאפשרות ל-CPU-ליבה 0 לקבוע אם הקוד הבא שיש לבצע מחוץ ל-bootROM הפנימי הינו מאובטח, ע"י בדיקת הקוד החתום באמצעות ערכי מפתח שכלולים בבלוק הנתיכים הפנימי. החל מאתחול מאובטח זה, מפתחי המערכת יוכלו לוודא שרשראות אתחול מאובטח סבירות של הרשאה, ויאפשרו לאשר טרם ביצוע אתחול ראשוני, hypervisor ואו/RTOS וכל תוכנת מערכת אחרת שפועלת במחיצות רבות.

תמיכה בספקי אוויוניקה – יוזמת MCFA

Freescale היא ספקית מעבדים לציוד A&D זה מספר עשורים. מעמדה זה הוביל להקמת קבוצת עבודה בסוף 2010 שכללה יצרנים של רכיבי אוויוניקה מסחריים באמריקה הצפונית ובאירופה.

קבוצת העבודה לריבוי הליבות לתעופה (MCFA) הוקמה כדי לסייע ליצרנים של רכיבי אוויוניקה לאשר ציוד העושה שימוש במערכות על שבב. באמצעות קבוצה זו, נוצרה שותפות בין יצרן מערכת על שבב לבין תעשיית האוויוניקה שמטרתה להגדיר את מערכת הנתונים הנדרשים בשלבי הפיתוח והאישור בתחומים שונים לרבות שיתופי פעולה טכניים ממוקדים, תכנון ואישור מערכת על שבב וניסיון במתן שירותים.