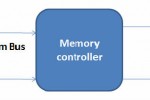

בסביבת מערכת על שבב (SoC), יש מודולים ספרתיים ואנלוגיים מרובים משולבים יחד על שבב יחיד, עם מעבדים וסוגים שונים של זיכרונות, המנוהלים על ידי בקרי זיכרון רגילים. בקרים אלו מנהלים את זרימת הנתונים בין ההתקנים ההיקפיים לזיכרונות ובין המעבד לזיכרונות. איור 1 מסביר את זרימת הנתונים הבסיסית בין המעבד לזיכרון.

הצורך בבקרי זיכרון חכמים

חידושים קבועים בטכנולוגיה הובילו לשיפורים המגיעים ל-60% כמעט (מדי שנה) בביצועים של המעבדים. עם זאת, השיפורים בביצועי הזיכרון איטיים באופן יחסי. כתוצאה מכך, הביצועים האיטיים יחסית של הזיכרונות ושל הבקרים שלהם, משפיעים על הביצועים הכוללים של המערכת על שבב. לדוגמה, ככל שקצב ביצוע הוראות המשיך לעלות, הדרישה לרוחב פס של הזיכרון גדלה באופן יחסי. מלבד זאת, התנהגות המעגל המשולב (IC) תלויה בתנאי התהליך, המתח והטמפרטורה (PVT) ובתדירות הפעולה. שינוי בתנאי PVT אלו יכול להוביל לבעיות של סנכרון ושל אישורי העברת מידע ("לחיצת ידיים") בין המעבד לזיכרון, שיגרמו לביצועים גרועים של המערכת על השבב. בקר חכם, עם זיכרון ניתן לקונפיגורציה ברמה גבוהה, יכול היה לפתור את הבעיות שמציבים הפרמטרים לעיל.

בקר זיכרון חכם מאפשר לתכנת בקונפיגורציה את התכונות השונות הבאות, על מנת לקבל ביצועים משופרים של המערכת על שבב ופתרון הבעיות המוזכרות לעיל:

1. בקרה של מצבי המתנה לקריאה (RWSC)

2. בקרה של צינור נתוני כתובות (APC)

3. אזורי זיכרון זמני והבאה מוקדמת של זיכרון מטמון

4. מיפוי כתובות מחדש

במאמר זה, נדון בשתי התכונות הראשונות של בקרי זיכרון.

בקרה של מצבי המתנה לקריאה (RWSC)

המונח RWSC מציין את מספר מצבי ההמתנה שיש להוסיף לזמן הגישה לקריאות ממערך הזיכרון במקרה הטוב ביותר. זמן הגישה לקריאות ממערך הזיכרון במקרה הטוב ביותר הוא מחזור אחד.

את המספר הזה יש לקבוע לערך התואם את תדירות הפעולה של בקר הזיכרון ואת זמן הגישה לקריאה בפועל של בקר הזיכרון.

הגישות לקריאה מסתיימות תחת בקרה של הגדרות מצבי המתנה מתאימות. לכן, זמן הגישה של הפעולה נקבע על ידי הערך RWSC. קביעת ההגדרה הנכונה של ערך RWSC יכולה לשנות את תזמון הגישה כדי לקחת בחשבון את תנאי הפעולה (תדירות, מתח, טמפרטורה) של המערכת על השבב.

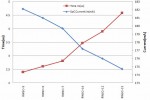

איור 2 מציג את ההשתנות של זמן הביצוע וההשתנות של הזרם על סיליקון בתלות בערכי RWSC.

מתוך הגרף לעיל, ברור שזמן הביצוע גדל עם הגידול בערכי RWSC, ככל שעולה הזמן הנדרש להבאת ההוראה. בהתאמה, ככל שמספר ההוראות המתבצעות לכל יחידת זמן יורד, הזרם יירד (עיין בגרף לעיל).

על מנת לשפר את ביצועי המערכת, אפשר להגדיר בקונפיגורציה בצורה נכונה את ערכי RWSC באמצעות תוכנה, בתלות בתנאי התהליך, המתח והטמפרטורה (PVT), אשר משפיעים על ההתנהגות של המערכת על השבב. באותו זמן, אפשר לנצל את ערכי RWSC כדי להשתמש בסוג מסוים של זיכרון עבור טווח רחב יותר של תדירויות מערכת, על ידי הגדרה בקונפיגורציה באופן מיטבי את הפרמטר RWSC. לדוגמה, אם זיכרון תומך במהירות של 16 מגה הרץ והמעבד או המערכת שברשותנו פועלים ב-100 מגה הרץ (שהיא משתנה מפני שהתקנים שונים דורשים תדרי מערכת שונים), יהיה לנו צורך בגשר ניתן לתכנות בין המעבד לזיכרון, שיוכל לבצע סנכרון של המערכת.

בקרה של צינור נתוני כתובות (APC)

בבקר זיכרון בריבוי חיבורי port, משתמשים בבקרת APC כדי לבקר את מספר המחזורים לפני שאפשר לאתחל את קריאת הזיכרון הבאה מחיבור port של בקר הזיכרון הנגדי, לפני שיהיה תיקוף של נתוני הקריאה הקודמים בחיבור הנוכחי. דבר זה ישים כאשר בקרי שליטה מרובים של אפיק מערכת מנסים לגשת אל אותו זיכרון דרך בקרי הזיכרון.

גישות למערך הזיכרון יכולות להיות מועברות בצינור נתונים (pipelined) על ידי כתובת גישה עוקבת ואותות בקרה, תוך כדי המתנה עד אשר הגישה הנוכחית תסתיים. העברה בצינור נתונים של גישה לזיכרון מאפשרת ביצועים משופרים על ידי הקטנת זמן אחזור הגישה, הנראה על ידי בקר השליטה של אפיק AHB.

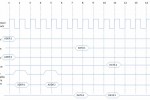

העברה בצינור נתוני כתובות מתוארת באיורים 3 ו-4, המציגים גישה בסיסית לקריאה של ריבוי בקרי שליטה בחיבור Port 1 ובחיבור port 2 של בקר זיכרון, בו זמנית.

א. בשפת העלייה הראשונה של אות השעון, בקר הזיכרון לוכד את הכתובות משני בקרי השליטה (ADDR1 ו- ADDR2), וכתובת מחיבור port של בקר הזיכרון שיש לה עדיפות גבוהה יותר, תועבר ראשונה אל אפיק הכתובות בזיכרון, כלומר אל ADDR1.

ב. בשפת העלייה השנייה של אות השעון, הכתובת (ADDR1) נקלטת באפיק הזיכרון עם אותות בקרת אפשור הקריאה (Read Enable) מבקר הזיכרון.

ג. בשפת העלייה השביעית של אות השעון כאשר הנתונים יהפכו כבר יציבים ויופיעו באפיק הנתונים, רק בקר הזיכרון יעביר כתובת (ADDR2) אל אפיק הכתובות. לאחר זמן האחזור בבקר הזיכרון, הנתונים יועברו אל אפיק המערכת וייקלטו בשפת העלייה השמינית של אות השעון.

ד. בשפת העלייה השתים עשרה של אות השעון, לאחר זמן הגישה לזיכרון, הנתונים (DATA2) יופיעו באפיק הנתונים, ובשפת העלייה הבאה של אות שעון המערכת הם ייקלטו באפיק המערכת.

מכאן אפשר להבין שהכתובת עבור חיבור port 2 מועברת אל אפיק כתובות הזיכרון רק אחרי שהנתונים בחיבור port 1 נמצאו תקפים ורק לאחר הצעד הזה, תתחיל הגישה לקריאה עבור port 2.

כשצינור הנתונים מאופשר (איור 4) ההבדל מתבטא בצעד (ג) כאשר בקר הזיכרון שולח את הכתובת (ADDR2) ואת אותות הבקרה שלו שני מחזורי אות שעון לפני שהנתונים (DATA1) עוברים תיקוף. במקרה שבו ההעברה בצינור נתונים תהיה מושבתת, בקר הזיכרון ימתין שהנתונים יתייצבו או שיעברו תיקוף. לכן הנתונים (DATA2) מובאים מוקדם יותר בזכות זמן אחזור קטן יותר של הכתובת, ובכך מתקצר זמן האחזור לחיבור Port 2.

אם X באיור 3 הוא זמן האחזור להעברת כתובת (ADDR2) לזיכרון ו-Y הוא הזמן לקריאת נתונים (DATA 2), זמן הגישה הכולל הוא X + Y.

באיור 4, כשצינור נתוני הכתובת מאופשר, זמן אחזור זה, X, הוקטן מאחר שאנחנו מעבירים את הכתובת (ADDR2) לזיכרון במקביל מבלי להמתין לנתונים (DATA1) ובכך מתקצר זמן הגישה הכולל.

העברה בצינור נתונים בסיליקון

ההשפעה של העברת נתוני כתובת בצינור בסיליקון נראית בחיבור GPIO שמעביר ביצוע פקודות בין שתי ליבות, הניגשות בו זמנית לאותו זיכרון. באופן בסיסי שתי הליבות מעבירות חיבור GPIO אחרי ביצוע של מספר פקודות נתון ושווה. שפות העלייה של צורות הגל של שתי הליבות מופיעות תמיד באותו הפרש זמנים כתוצאה מאופן הביצוע הסדרתי, כלומר ליבה 2 (Core 2) תתחיל את הגישה שלה לקריאה רק אחרי שליבה 1 (Core 1) השלימה את הגישה לקריאה מהזיכרון ולהפך.

שפות העלייה של צורות הגל של שתי הליבות מופיעות בהפרש משתנה של מרווחי זמן. שפות העלייה של ליבה 1 אינן מופיעות רק אחרי אלו של ליבה 2 אלא מוזזות שמאלה כלומר השפות מופיעות מוקדם יותר, עובדה המראה על ביצוע פקודות בהעברה בצינור נתונים. מאחר ששפות העלייה של ליבה 1 מופיעות מוקדם יותר זמן האחזור עבור ליבה 1 מתקצר.

מסקנות

אפשר לשפר במידה רבה את הביצועים ואת השימוש בזיכרון במערכות על שבב על ידי בחירה בקונפיגורציה מתאימה של בקרי זיכרון חכמים, כפי שמתואר לעיל.

לסיכום, להלן היתרונות של שתי התכונות שבהן דנו במאמר זה:

RWSC –

א. אפשר לשנות את תזמוני הגישה לזיכרון בהתאמה לתנאי הפעולה של המערכת על שבב (תדירות, מתח, טמפרטורה) על הגדרה נכונה של RWSC (מצבי המתנה) שאת הקונפיגורציה שלהם אפשר לקבוע בתוכנה.

ב. אפשר ליצור את המספר המיטבי של מצבי המתנה עבור ביצועי מערכת משופרים וצריכת זרם משופרת.

APC –

בקרי זיכרון מרובי חיבורי port יכולים לשפר במידה רבה את הביצועים של מערכת על שבב על ידי העברת נתוני הכתובות והנתונים בצינור נתונים.

- איור 1. זרימת נתונים בסיסית בין המעבדים לזיכרון

- איור 2. זמן ביצוע עם ערכים שונים של RWSC

- איור 3. צינור נתונים מושבת (disabled)

- איור 4. צינור נתונים מאופשר