אתם מכירים את ההרגשה, כאשר הבוס שלכם מדווח כי נוסף מוצר חדש לתחרות שהוא קטן יותר, קל יותר, מהיר פי שתיים וצורך פחות הספק. ותוסיפו לכך בקשה מההנהלה לפתח ולמכור מוצר טוב יותר בתוך שישה חודשים.

ובכן, זהו אתגר. היסטורית, ארכיטקטי מערכת ניסו לארוז יותר רכיבים נפרדים על לוח מעגל מודפס סטנדרטי, בניסיון לספק פונקציונאליות וביצועים מקסימליים תוך שמירה על תקציב ההספק הנדרש. פתרון קונבנציונאלי מסוג זה מגיע היום לנקודת מיצוי לוגי כיוון שהיא נאבקת לעמוד בדרישות הדור הבא.

חלק מהאתגרים המרכזיים היום הם:

רוחב פס בין רכיב לרכיב (Chip-to-chip) מוגבל על ידי צפיפות החיבור האפשרי ע"י מוליכי ה-PCB.

הספק המערכת גבוהה מידי בשל הצורך להשתמש במוליכים ארוכים עבור חיבור הרכיבים על ה-PCB (קיבוליות גבוהה).

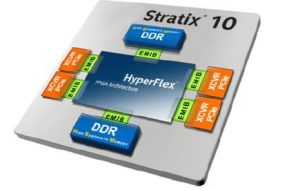

איור 1. טכנולוגיית אינטגרציה במארז רבגונית 3D SiP

תצורת מערכת מסוג זה של PCB תהיה לעולם גדולה מידי בשל הצורך בשימוש במספר רכיבים נפרדים גדול לשם פונקציונאליות המערכת הנדרשת.

ארכיטקטי המוליכים למחצה חיפשו פתרון למגבלות אלו על ידי שימוש באינטגרציה מונוליטית. למרות זאת, אינטגרציה זו מובילה ישירות לאתגר חדש: בשלות ה-IP. אינטגרציה איננה אפשרית תמיד, לדוגמה, תקחו זכרון DRAM: זכרון זה נבנה על ידי שימוש בתהליך טכנולוגי של 40nm או יותר. הגבלה זו אינה מקלה על פתרון מונוליטי אם רוצים להשתמש בתהליך 14nm. אתגר מרכזי נוסף הוא הצורך לספק מהירות חיבור גבוהה ככל הניתן בין התקנים. היסטורית, יצרני FPGA הגיבו באמצעות מינוף טכנולוגיות קצה של מקמ"שים (transceivers). הדור הבא של התקנים מתכנתים כגון Stratix® 10 FPGA וכן מערכות על רכיב (SoCs) מתבסס על הובלה טכנולוגית זאת ומתוכנן לתמוך בקצב העברת נתונים של עד 56Gbps, עם תוכניות אפנון כמו PAM-4. למרות זאת, פרוטוקולי ביצועים גבוהים, ומכך IP blocks מוקשחים הקשורים אליהם, מתפתחים ללא הרף, לפיכך הכרחי להגדיר פתרונות רכיבי FPGA חדשניים אשר מאפשרים לשלב בצורה פשוטה ומהירה IP blocks קשיחים עם פרוטוקולים טכנולוגיים חדשים.

אינטגרציה במארז תוך שימוש בטכנולוגיית 3D SiP רבגונית

טכנולוגיית מערכת תלת מימדית במארז (3D SiP) עם רכיבי Stratix® 10 FPGA ו-SoCs עונה על האתגרים הבאים: רוחב פס גבוה יותר, הספק נמוך יותר, גורם תצורה קטן יותר ועלייה בפונקציונליות ובגמישות. כמו כן טכנולוגיה זו מאפשרת אינטגרציה במארז אשר ניתנת למימוש וייצור פשוט יותר. הטכנולוגיה הרבגונית 3D SiP מאפשרת אינטגרציה במארז לטווח רחב ומגוון של רכיבים כגון: אנלוגי, זיכרון, ASIC CPU ועוד. (ראה איור 1). בנוסף טכנולוגיה זו יכולה לשלב רכיבי סיליקון מתהליכי ייצור שונים באותו מארז.

עבור המקמ"שים, הטכנולוגיה הרבגונית

איור 2. המבנה העקרוני של טכנולוגייה אינטגרציה במארז רבגונית 3D SiP

3D SiP מאפשרת הפרדה של סיליקון המקמ"שים (אריח – tiles) מסיליקון ליבת ה-FPGA: כלומר, שהסיליקון של המקמ"שים וה-FPGA כבר לא מוכרחים להיות מיוצרים באותו תהליך ליטוגרפי.

איור 2 מציג את המבנה העקרוני של פתרון מערכת על מארז.

הטכנולוגיה הרבגונית 3D SiP מאפשרת לערבב רכיבים על מנת להתאימם לדרישות המערכת, ובכך לספק בצורה אפקטיבית פתרונות עמידים בצורה מהירה יותר מאשר בדורות הקודמים. רכיבי Stratix 10 ממנפים פתרונות מקמ"שי IP מוכחים, הורדה משמעותית בצורך לתיקוף ושיפור זמנים דרמטי של הלקוחות בזמן ההבאה לשוק של מוצרים. במבט קדימה, טכנולוגיית ה-3D SiP מספקת פתרונות מדרגיים אשר תומכים במקמ"שים במהירות של 56Gbps עם תוכניות אפנון מתעוררות כגון PAM-4. באופן דומה, אריחי מקמ"שים נפרדים מאפשרים לתמוך ב-IP משובצים מותאמים. לדוגמה, אריחי מקמ"ש ראשוניים של Stratix 10 כוללים PCIe* Gen3 x16 hard IP block. גרסאות עתידיות יכולות באופן פוטנציאלי לתמוך במגוון של מודלי IP מוקשחים, כגון PCIe* Gen4, פורטי אי-טרנט מרובים, ממשקים אופטים ועוד. הטכנולוגיה אשר הופכת הטמעה רחבה כזו לאפשרית היא פטנט מוכר הנקרא state-of-the-art Embedded Multi-die Interconnect Bridge1below .

EMIB מציע צפיפות גבוהה במיוחד לחיבוריות בין רכיבי סיליקון רבגוניים במארז אחד. בנוסף מאפשרת הטכנולוגיה פונקציונאליות תוך מארזית אשר היתה מורכבת מידי או יקרה מידי ליישום באמצעות טכנולוגיות ריבוי-סיליקון חלופיות.

יתרונות ה-EMIB

בהשוואה לתהליכים חלופיים טכנולוגית EMIB מציעה תהליך ייצור פשוט יותר, ביצועים גבוהים יותר, הקטנת מורכבות ושיפור אותות והספקים משולבים.

איור 3 מתאר את מבנה המארז הפיזי. המבנה מראה אינטגרציה רבגוניות של מארג סיליקון ה-FPGA ושני סיליקוני מקמ"שים (2). שלושת יחידות הסילקון נחות על מערך סטנדרטי של כדורי flip-chip הנמצאים על מצע המארז (3), אשר מחובר לבסיס ה-PCB. הנתיבים בין הסיליקון לכדורי המארז משתמשים בנתיבי FCBGA סטנדרטיים (4). הרכבה זו ארוזה כמכלול אחד עם מכסה אריזה (5) על מנת ליצור פיתרון סגור אחד. מצע המארז מיישם מספר חיבורי EMIB .

EMIB הוא שבב סיליקון קטן המשובץ בתחתית מצע המארז ומציע צפיפות גבוהה במיוחד על ידי קישוריות בין יחידות הסיליקון. חשוב לציין, הממדים הפיזיים של EMIB לא מגבילים את הכמות או המיקום של יחידות הסיליקון שיכולות להיות משולבות. לעומת זאת, יישום חליפי משתמש בחלק גדול של הסיליקון כחוצץ אשר ממוקם בראש מצע המארז וגורם לחריגה ביחס אורך ורוחב של הסיליקון. חוצץ הסיליקון הגדול הופך את הפתרון ליקר ולכן הינו חסם תמחירי אשר נוטה לבעיות. פתרון חוצץ זה דורש בנוסף שימוש בכמות גדולה של רכיבי מיקרו, אשר משפיעים גם כן על הנצילות הכללית שניתן להשיג מהסיליקון, לפיכך יכולה להשפיע משמעותית על המחיר ומורכבות הייצור. מספר יחידות הסיליקון אשר יכולות להיות מושלבות כאשר משתמשים בחוצץ מוגבל, וכן משפיעים על המדרוג והגמישות. תהליך ה-EMIB לעומת זאת מקטין משמעותית את מורכבות הייצור.

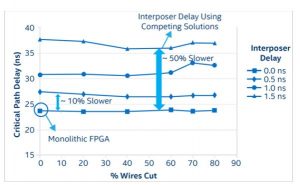

איור 3. אינטגרציה רבגונית באמצעות שימוש בטכנולוגית EMI

המארג המונוליטי של ליבת ה-FPGA הוא קריטי להספקת ביצועים וניצולת מקסימליים על ידי הבטחה כי הנתונים יכולים להיות מעובדים בקצב הגבוהה ביותר האפשרי מבלי להיתקל בעומס נתיבים או צווארי בקבוק. עם תהליך טכנולוגי 14nm Tri- Gate וארכיטקטורת HyperFlex™ FPGA החדשה של אינטל, מארג ה-FPGA יכול לספק יעדי ביצועים של 2X בממוצע בהשוואה לדורות קודמים של FPGA מהקצה העליון. איור 4 משווה התקן עם מארג מונוליטי, כמו Stratix 10 FPGA, עם מוצר מתחרה שמחלק את המארג המונוליטי של ה-FPGA למספר פיסות סיליקון נפרדות ולאחר מכן מחברים אותם חזרה באמצעות טכנולוגיות מבוססות חוצצים. תוצאות של מחקר עצמאי מראה כי ירידה משמעותית בביצועים מתרחשת כאשר מחברים מארג FPGA לוגי באמצעות חוצצים. עם השהיית חוצץ אופיינית של 1.5ns יכולה להיות ירידת ביצועים של עד 50% במארג בנתיב הקריטי של ה-FPGA בהשוואה לפתרון מונוליטי טהור2.

איור 4. ירידה בביצועי FPGA בהשוואה למארג מונוליטי

לכן, בפעם הבאה שתתבקשו לעשות את הבלתי אפשרי, תהיה אפשרות נוספת בארגז הכלים שלכם. רמת האינטגרציה שתקבלו מ-FPGAs Stratix 10 ו-SoCs, המננפים את טכנולוגיית EMIB המוגנת בפטנט, מאפשרת לכם ליצור פתרונות שמגדילים את המדרוג, מפחיתים את הסיכון ומורידים את זמן היציאה לשוק. בנוסף, FPGAs Stratix 10 ו-SoCs משלבים את טכנולוגיית Tri-Gate 14nm עם טכנולוגיית HyperFlex FPGA החדשה והליבה המונוליטית. Stratix 10 FPGAs ו-SoCs מבטיחים לחולל מהפכה לנוף פלטפורמות הדור הבא.

*הכותב הינו מנהל מוצר בכיר בחטיבת הרכיבים המתכנתיים של אינטל בסאן חוזה.

הפניות:

- http://www.intel.com/content/www/us/en/foundry/emib.html

- CADandRoutingArchitectureforInterposer-BasedMultiFPGASystemsbyAndreHahnPereira, UniversityofSaoPauloandVaughnBetz, UniversityofToronto.

* PCI-SIG® and PCIe® are registered trademarks and/or service marks of PCI-SIG