בעולם של ימינו, מיקרו-בקרים גדולים עם 32 סיביות (MCU) ומיקרו-מעבדים (MPUs) שמריצים מערכת הפעלה בזמן אמת (RTOS) הופכים לנפוצים יותר ויותר. עם זאת, ייתכן שמשאבי המעבד של מיקרו-בקר גדול יחיד שמטפל באפליקציה מורכבת לא יספיקו לטיפול במשימות תחזוקה קטנות, שאינן מורכבות, אך גוזלות זמן.

ניתן להשתמש במכשירים קטנים יותר, כמו MCU עם 8 ו-16 סיביות כדי לשחרר עומס המשימות האלה ממכשיר ה-32 סיביות ולהניע חדשנות ופיתוח על פני הספקטרום של המיקרו-בקרים, כל הדרך מ-8 סיביות ועד 32 סיביות

ניתן לנהל משימות רבות ביתר קלות במכשיר ה-32 סיביות באמצעות העברת חלק מהמשימות הללו למעבדי משנה שמטפלים רק במשימה אחת או שתיים אך דורשים פיקוח מועט כשהם מבצעים אותן. הפעולה הזו מורידה את העומס ממשאבי ה-CPU במעבד הראשי, מפחיתה את מורכבות התוכנה ומשפרת את הביצועים ואת זמן הביצוע.

לדוגמה, ניתן להשתמש ב-MCU עם 8 סיביות כדי ליצור מרחיב I/O. מרחיבי ה-I/O אינם מכשירים מורכבים, אך הם צורכים הרבה זמן עיבוד בשל טיפולים תכופים בהפרעות. כשמשתמשים ב-MCU ייעודי למשימה הזו, מכשיר גדול יותר יכול להפחית את ניצול ה-I/O שלו ואת מספר ההפרעות שבהן הוא צריך לטפל. בנוסף, ערכת התכונות של מרחיב ה-I/O מוגדרת בתוכנה, כך ניתן להתאים ולכוונן אותה עבור האפליקציה.

הגמישות היא היתרון הגדול ביותר של יצירת מרחיב I/O באמצעות MCU עם 8 סיביות. מערך התכונות של מרחיב I/O nxud ASIC נוצר במכשיר, בעוד שה-MCU מגדיר את התנהגותו על סמך התוכנה שהוא משלים. הגמישות הזו מאפשרת לשנות את הגרסה המבוססת על MCU ולהתאים אותה לצרכי היישום הסופי.

הטמעת מרחיב ה-I/O המתקדם

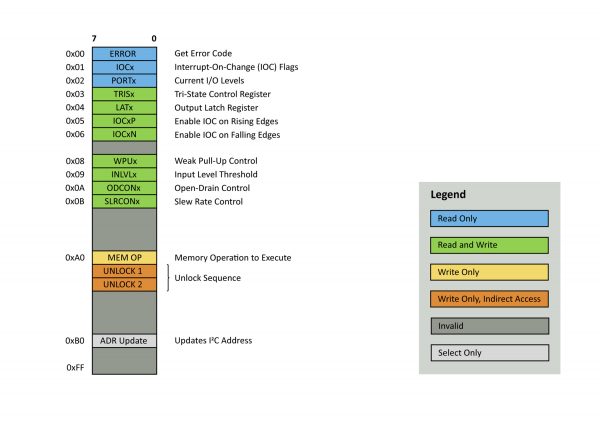

באופן פנימי, מרחיב ה-I/O המתקדם פועל במבנה שמבוסס על טבלת חיפוש. לפני הקריאה או הכתיבה נשלחת כתובת וירטואלית. הכתובת הזו אינה מתואמת עם הרשימות במיקרו-בקר – היא ספציפית רק לטבלת החיפוש. המשמעות היא שניתן להוסיף תכונות שאינן נמצאות ברישומי החומרה של המיקרו-בקר באופן שקוף. ניתן לארגן את הערכים מחדש בקלות בטבלה גם לטובת שימושים ספציפיים. יתרון נוסף של מבנה זה הוא היכולת להוסיף הרשאות לטבלת החיפוש. לדוגמה, כדי ליצור רשימה לקריאה בלבד, אפשר פשוט להשמיט את ערך הכתיבה טבלת חיפוש.

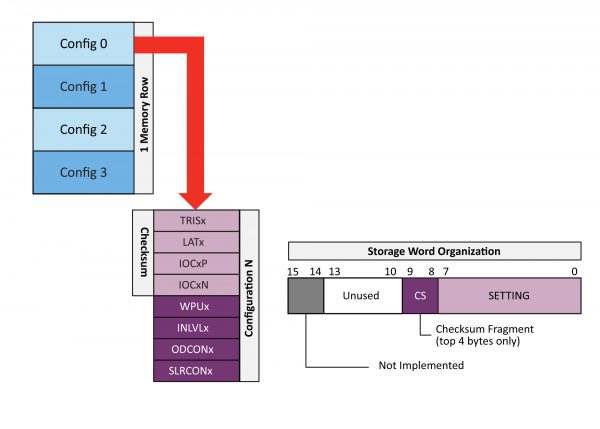

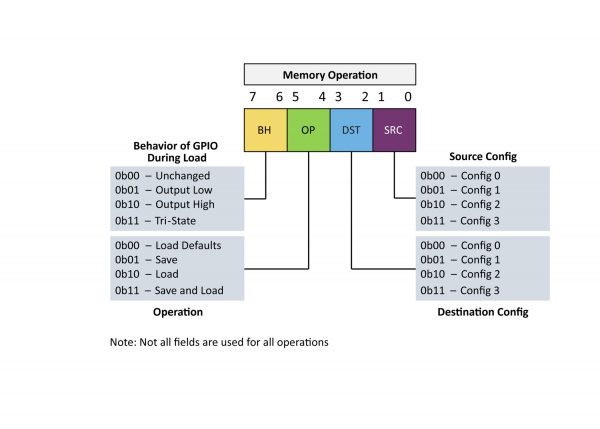

המבנה הזה מורכב יותר והוא מתאים גם לפונקציות לא סטנדרטיות. הפונקציה “MEM OP” מאפשרת ל-MCU לשמור בזיכרון או לטעון ממנו את תצורת General-Purpose Input and Output (GPIO) הנוכחית.

בנוסף, MEM OP יכול לאפס את תצורת ה-GPIO לפרמטרים שנקבעים בעת הקימפול

פונקציונליות של MEM OP

לחלופין, ניתן להגדיר את המיקרו-בקר לטעון את ההגדרות השמורות כשמדליקים אותו. אם ההגדרה מופעלת, המיקרו-בקר מנסה לטעון את ההגדרות בתצורת 0. אם התצורה נכשלת באימות סכום הביקורת, ה-MCU יחזור לקמפל בזמנים קבועים. אם אין בה צורך, ניתן להשבית את התכונה הזו מתוך התוכנה.

היתרון של פתרון מבוסס MCU הוא הגמישות הקיצונית שהוא מספק. בניגוד ל-ASICs שקיימים בשוק, ניתן להגדיר את ה-MCU עם פונקציות לא סטנדרטיות באופן ספציפי לאפליקציה שנמצאת בשימוש. היישום הזה פותח עבור משפחת CUs PIC16F15244 לשימוש כללי. קוד המקור זמין ב- Discover Microchip(discover.microchip.com) וב-Github.

ממיר מתח לתדר (V/F).

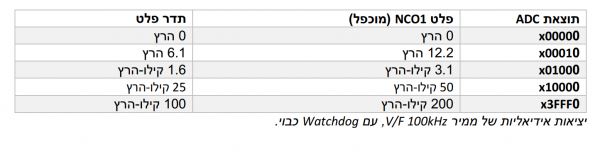

ממיר המתח לתדר (V/F) ממחיש את השימוש בציוד היקפי לחומרה כדי ליצור פונקציה שבדרך כלל נצטרך ליצור באמצעות מעגל משולב חיצוני ללא תלות בליבה. אחד היתרונות הגדולים ביותר של התצורה הזו הוא שהציוד ההיקפי מוגדר בתוכנה, כך שניתן לשנות את הדוגמה ביתר קלות. יתרון נוסף הוא העובדה שהממיר מוטמע במיקרו-בקר, כך ניתן להפחית את עלות החומרים (BOM) ואת שטח התכנון הנדרש.

אחד האתגרים של הגישה המבוססת על MCU הוא שהיא לא מתפקדת כמו הפתרון האנלוגי משום שה-ADCC מגביל את הרזולוציה של הפלט באופן מהותי. באופן נומינלי, ה-ADCC הוא ברזולוציית 12 סיביות, אך מוגדר לרזולוציית יתר של 14 סיביות. כמו כן, למתנד מבוקר נומרי (NCO) המובנה שמסנתז את תדר המוצא יש רזולוציה סופית וייתכן שיש בפלט שלו ריצוד, בהתאם לערך שנמדד על ידי ה-ADC.

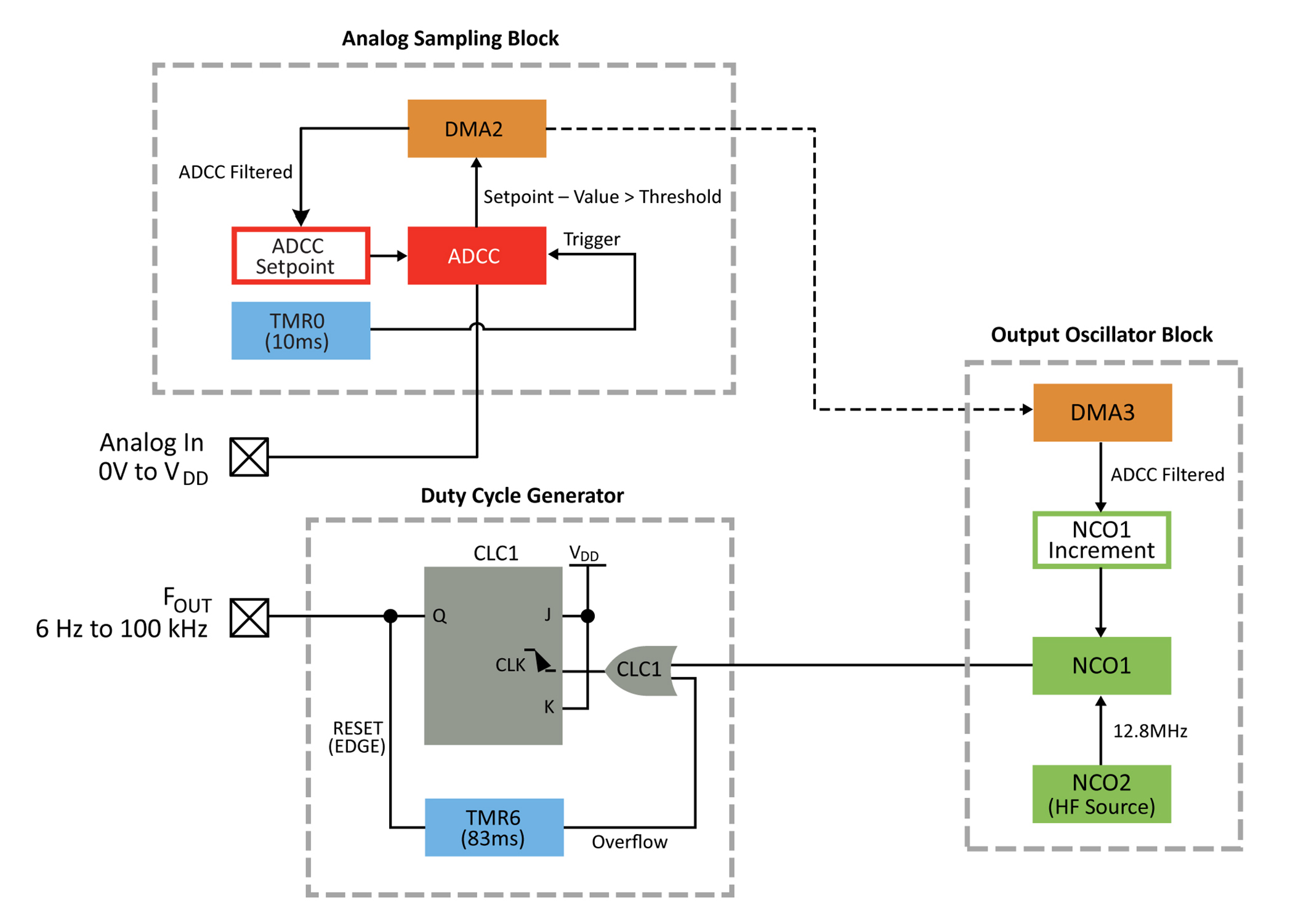

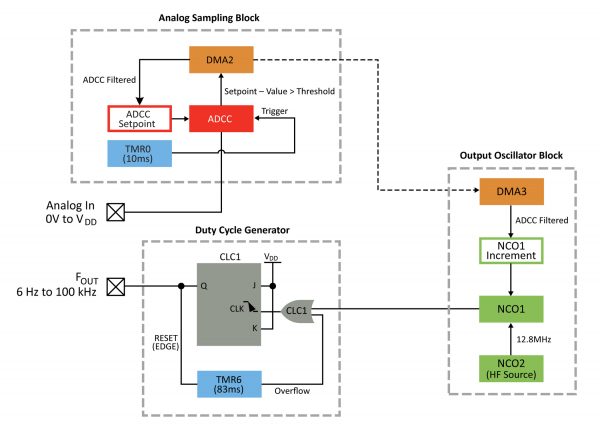

כדי להטמיע את הפתרון זה, ישנם שלושה בלוקים נפרדים של ציוד היקפי – בלוק דגימה אנלוגי, בלוק מתנד פלט ומחולל מחזור עבודה.

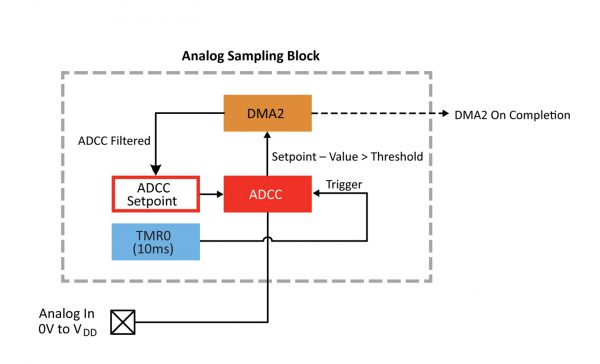

בלוק דגימה אנלוגי

בלוק הדגימה האנלוגי אחראי להמרה מאנלוגי לדיגיטלי. כדי שתהיה אפשרות ליצור פלט של 100 קילו-הרץ במגבלות התדר של המכשיר, ה-ADCC הוגדר לצבור דגימות מרובות ולאחר מכן ליצור ממוצע כדי לקבל תוצאה של דגימת יתר בגודל 14 סיביות.הטמעת בלוק דגימה אנלוגי

החיסרון בדגימת יתר זו הוא הרעש הסטטיסטי שנוסף לתוצאה. יצירת הממוצע של דגימת היתר והוספת ההיסטרזיס מפצים על הרעש. כדי להטמיע היסטרזיס, נשתמש בתכונת הפסקת הסף של ה-ADCC. (למען הפשטות, נעבור רק על פרטי האופן שבו נעשה שימוש בתכונת הפסקת הסף בדוגמה זו).

כאשר ה-ADCC מסיים לחשב את דגימת היתר הממוצעת, הערך המתקבל מושווה לרישום של נקודות קבע בציוד ההיקפי. אם ההבדל בין השניים גדול או קטן מהסף שנקבע, מופעלת הפסקה. ה-CPU מסווה את ההפסקה הזו והיא אינה מושפעת, אך היא מפעילה עותק גישה ישירה לזיכרון (DMA) של תוצאת דגימת היתר הממוצעת לרשימת נקודות ההגדרה של ה-ADCC, שמעדכן את נקודת האמצע של ההיסטרזיס. אם אין חריגה מהסף, עותק ה-DMA לא ייווצר וה-DMA של בלוק מתנד הפלט לא יתעדכן.

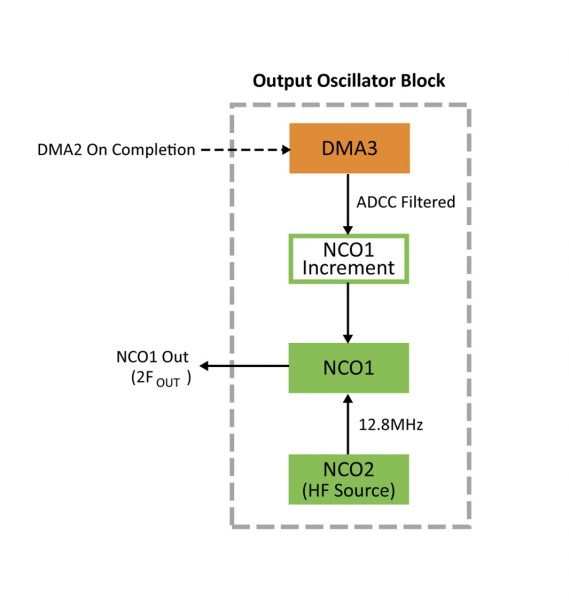

מבנה בלוק מתנד הפלט

בלוק מתנד הפלט של פתרון זה אחראי על יצירת אות שעון בתדר הפלט הרצוי. אות הפלט הזה מחובר באופן פנימי למחולל מחזור העבודה, החיבור הזה מפחית את תדר הפלט בחצי אך יוצר פלט של 50% ממחזור העבודה. בשל כך, בלוק מתנד הפלט פועל בתדירות כפולה מהפלט.

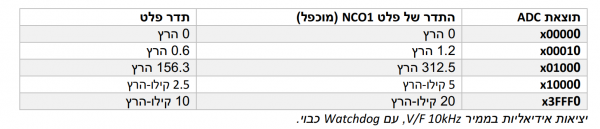

הלב של בלוק מתנד הפלט הוא מתנד מבוקר נומרי (NCO). הציוד ההיקפי של NCO פועל באמצעות הוספת ערך הפרש קבוע באקומולטור בקצה העולה של שעון קלט. הצפת האקומולטור משמשת להפקת הפלט של הציוד ההיקפי. (להסבר המלא על NCO, יש לעבור על גיליון הנתונים.)

בדוגמה זו, NCO2 הוגדר כדי ליצור את תדר שעון הכניסה הנדרש באופן פנימי כדי לקבל פלט של 100 קילוהרץ מקלט של 14 סיביות. אנו משתמשים בתוצאה של 14 הסיביות מכיוון שתוצאת 12 הסיביות המקורית מה-ADCC אינה גדולה מספיק כדי ליצור פלט של 100 קילו-הרץ ללא מקור שעון חיצוני.

אם תדר הפלט של NCO2 משתנה, או שנעשה שימוש במקור חלופי, תדר הפלט ישתנה לטווח פלט אחר. לדוגמה, אם NCO2 מופחת ל-1.28 מגה-הרץ, התפוקה תהיה 10 קילו-הרץ לכל היותר.

תרשים בלוק של מחולל מחזור העבודה

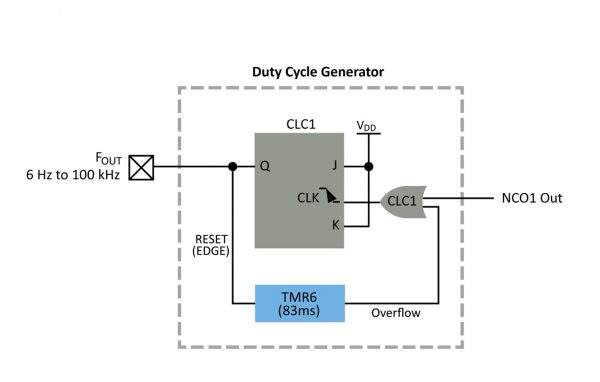

בלוק מחולל מחזור העבודה של פתרון זה אחראי ליצירת תפוקת מחזור עבודה של 50%. התכונה זו היא אינה חובה – ניתן להשתמש בפלט מה-NCO ישירות, אך מחזור העבודה ישתנה במידה גדולה הרבה יותר.

המחולל הזה מוטמע באמצעות אחד מה-Configurable Logic Cells (CLC). ה-CLCs הם בלוקים קטנים של לוגיקה נבדלת שניתנת להגדרה, בדומה לתא בודד של Field Programmable Gate Array (FPGA). ניתן להשתמש ב-CLC כשערים לוגיים נבדלים, למשל AND-OR או OR-XOR. ניתן להגדיר אותם גם כמנעולים או כפליפ-פלופ. בפתרון זה, הוטמע CLC כפליפ-פלופ J-K עם איפוס. J ו-K נשמרים בלוגיקת HIGH. בלוק מתנד הפלט משמש כשעון לפליפ-פלופ. כל פעימת שעון קלט גורמת להחלפת הפלט, כך נוצר מחזור עבודה של 50%. הערה: ריצוד תדר מבלוק מתנד הפלט ישפיע על מחזור העבודה.

טיימר 6 משמש כטיימר “watchdog” יציב. אם הפלט לא מייצר קצה (עולה או יורד), הטיימר יוצף וייצר פעימות שעון ל-CLC. הוא שולט בצד הנמוך של טווח תדר הפלט. במקום להגיע ל-DC, הפלט מתחלף לפלט של 6 הרץ במחצית התדר של הטיימר.

כדי להטמיע את הדוגמה, בחרנו במשפחת MCUs PIC18-Q43 בשל כמות הציוד היקפי הגדולה שנמצאת בשימוש. קוד המקור לפרויקט זה זמין ב- Discover Microchip(discover.microchip.com) וב-Github.

סיכום

בעוד שמיקרו-בקרים ומיקרו-מעבדים בעלי ביצועים גבוהים צפויים להישאר בסביבה, MCU עם 8 ו-16 סיביות הם כלים רבי ערך לביצוע משימות קטנות שדורשות מומחיות. המשימות אינן בהכרח מורכבות, אך הן עשויות לגזול זמן או להיות קריטיות. כשמפחיתים את עומס המשימות, מכשירים עם 32 סיביות יכולים לקבל יישומים פשוטים יותר שמשפרים את האמינות, מפחיתים את השימוש בזיכרון ובעלי צריכת החשמל נמוכה יותר.