כללי

מאמר זה מספק את המתודולוגיה של ממירים מכוילים מספרתי לאנלוגי (DAC) ובמיוחד לדוחפי PIN אלקטרוניים, מעגלי השוואה (comparator), עומס, יחידת ניהול הספקים (PMU) ובמערכות עיבוד נתונים (DPS). לממירים מספרתי לאנלוגי יש תכונות של חוסר ליניאריות כגון אי ליניאריות בגזירה (DNL) ואי ליניאריות באינטגרציה (INL), שאותם אפשר למזער בעזרת כוונוני הגבר והיסט (offset). במאמר זה מתוארת הדרך שבה אפשר לבצע את התיקונים האלה לשיפור ביצועי הגדרת הרמה.

מבוא

ציוד בדיקה אוטומטי (ATE) מתאר מכשיר בדיקה המתוכננים לבצע רצף יחיד של בדיקות על התקן יחיד או על התקנים מרובים בזמן נתון. סוגים שונים של ציוד בדיקה אוטומטי בודקים מערכות אלקטרוניות, חומרה והתקני מוליכים למחצה. התקני תזמון, ממירי DAC, ממירי ADC, מולטיפלקסרים, ממסרים ומתגים הם הבלוקים התומכים במבדק או במערכת ציוד הבדיקה (צב"ד) האוטומטי. התקני אלקטרוניקת PIN אלו יכולים לספק אותות והספק בערכים מדויקים של מתח וזרם. התצורה של אותות מדויקים אלו נקבעת על ידי ממירי DAC לקביעת הרמה. בתיק מוצרי הצב"ד האוטומטי, לחלק מהתקני אלקטרוניקת PIN יש אוגרי כיול וחלק מהגדרות הכיול מאוחסנות מחוץ לשבב. במאמר זה מתוארים הפונקציה, השגיאות והכיול של ממיר DAC דרך כיווני ההגבר וההיסט.

ממיר מספרתי לאנלוגי (DAC)

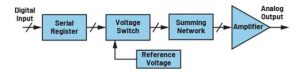

ממיר מספרתי לאנלוגי הוא סוג של ממיר נתונים אשר ממיר כניסות לרמות המוצא האנלוגיות המתאימות. ממיר DAC בעל N סיביות יכול לתמוך ב–2 בחזקת n רמות במוצא. מספר גבוה יותר של סיביות תואם לרזולוציה גבוהה יותר במוצא של ממיר DAC.

איור 1. תרשים בלוקים של ממיר מספרתי לאנלוגי (DAC). קרדיט: ANALOG DEVICES

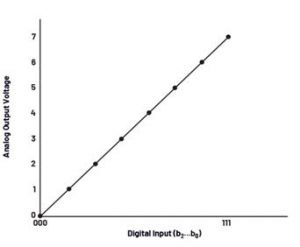

ראשית, הכניסה הספרתית בת N סיביות מועברת אל אוגר טורי של ממיר DAC. מתג המתח ורשת הסיכום בנגדים ממירה את הכניסות הספרתיות לרמות מוצא אנלוגיות. תרשים מאפייני ההעברה של ממיר DAC מוצג באיור 2. בממיר DAC לשלוש סיביות, כניסה ספרתית של 2 בחזקת 3 מניבה שמונה רמות מוצא אנלוגי.

איור 2 :פונקצית מעבר אידיאלים של

ממיר DAC ל–3 סיביות. קרדיט: ANALOG DEVICES

שגיאות ממיר DAC

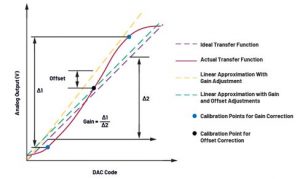

בעולם האמיתי, הממירים אינם אידיאליים. כתוצאה מהשונות בערכי ההתנגדות, באינטרפולציה ובדגימה, פונקצית התמסורת לא תהיה קו ישר או ליניארי. אל שגיאות אלו מתייחסים במפורש כאי ליניאריות בגזירה (DNL) וכאי ליניאריות באינטגרציה (INL). DNL הוא הסטייה המרבית של רמות המוצא מהגדלים האידיאליים של מדרגות. הוא נגזר מההפרש בין שתי רמות מתח עוקבות במוצא. INL הוא הסטייה המרבית במאפייני הכניסה והיציאה מפונקציית תמסורת אידיאלית. עם תיקוני שבח והיסט (offset) אפשר להקטין את שגיאות INL.

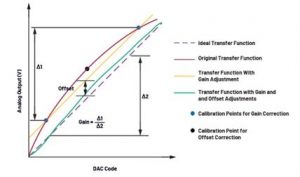

שגיאת INL המופיעה באיור 3 מציגה את הסטייה בין פונקצית התמסורת הממשית לבין פונקצית התמסורת האידיאלית. שגיאת השבח של ממיר DAC מציינת עד כמה השיפוע של הקירוב הליניארי של פונקצית התמסורת תואם לשיפוע של פונקצית התמסורת האידיאלית. כוונון ההגבר ישפיע על הזווית של הקירוב הליניארי כשהוא יוצג בגרף. שגיאת ההיסט היא ההפרש בין הערך הנמדד לבין נקודה נבחרת של היסט האפס הרצוי. כוונון של ההיסט יסיט בהתאמה את הקירוב הליניארי כולו כלפי מעלה או כלפי מטה. שגיאת INL של קוד יחיד היא הסכום של שגיאת ההגבר עם שגיאת ההיסט בנקודה מסוימת. אחרי כיול, אחרי ששגיאת ההגבר ושגיאת ההיסט הוקטנו למינימום, פונקצית התמסורת יכולה להיות קו שמשורטט בין נקודות הקצה.

איור 3 :פונקצית התמסורת של

שגיאת INL. קרדיט: ANALOG DEVICES

שגרת כיול

כדי להקטין מצבי אי ליניאריות של ממיר DAC המשתמש יכול לקבוע שגרת כיול באמצעות תיקוני שבח והיסט. התהליך הבא מסביר צעד אחר צעד את תהליך שגרת הכיול לדוגמה.

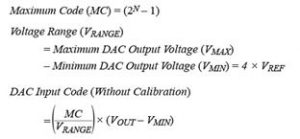

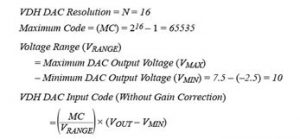

עבור ממיר DAC בעל N סיביות:

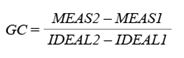

◄ תיקון שבח (GC):

לממירים מספרתי לאנלוגי יש נטייה להפוך ולהיות פחות ליניאריים בערכים הבינריים הנמוכים והגבוהים. לכן מומלץ לבחור נקודות כיול בתחום 5% עד 10% בין הערכים הבינריים הקיצוניים או בנקודות הכיול המומלצות בטבלת EC.

- קבע את הכניסה של ממיר DAC לערך שהוא 5% מעל הערך הבינרי הנמוך ביותר. חשב את ערך מתח המוצא הצפוי ורשום אותו בתור IDEAL1. מדוד את מתח המוצא ורשום אותו בתור MEAS1.

- קבע את הכניסה של ממיר DAC לערך שהוא 5% מתחת הערך הבינרי הגבוה ביותר. חשב ורשום את הערך של IDEAL2. מדוד את מתח המוצא ורשום אותו בתור MEAS2.

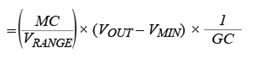

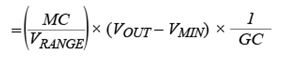

- הקוד בכניסת ממיר DAC (עם תיקון שבח)

◄ תיקון היסט (OC):

נקודת היסט אפס הרצויה משתנה לפי היישום. על המשתמש להגדיר את הערך הטוב ביותר בהתבסס על היישום שלו. ייתכן שחלק מהמשתמשים יעדיפו להשתמש במתח של אפס וולט כדי לקבל נקודת ייחוס מדויקת של האדמה. חלק מהמשתמשים יעדיפו להשתמש בנקודת האמצע של טווח הפעולה שלהם כדי למזער את שגיאת INL הכוללת.

- החל את תיקון השבח של ממיר DAC על השיפוע של משוואת ההמרה של מתח לקוד כדי לקבוע שבח יחידה.

- בחר את נקודת המתח הרצויה להיסט אפס ורשום אותה בתור IDEAL3. חשב את הקוד באמצעות המשוואה שלך להמרה של מתח לקוד. בצע תכנות של הקוד המחושב שלך ולאחר מכן מדוד את מתח המוצא ורשום אות בתור MEAS3.

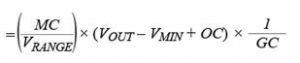

- הקוד בכניסת ממיר DAC (עם תיקוני שבח והיסט)

דוגמה 1

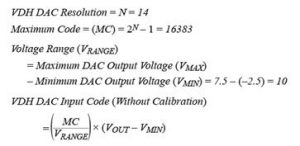

נבדוק את MAX32007, DCL מתומן עם ממיר DAC בעל יכולת כיוונון עצמית משולבת ומתגי יחידת ניהול הספקים (PMU). ל- MAX32007 יש ממירי DAC פנימיים עבור ערכי VDH, VDL, VDT/ VCOM, VCH, VCL, VCPH ו- VCPL לקביעת רמה. כדי לכייל את ממירי DAC, יש לעקוב אחר התהליך הבא:

◄ הפעל את ערכת ההערכה (EV) של MAX32007על ידי כך שתעקוב אחר ההוראות בדף הנתונים של ערכת ההערכה.

◄ חבר את מחברי SMB, DATA0A ו- NTRM0A למתח של 1.2 וולט.

◄ חבר את מחברי SMB, NDATA0A ו- TRM0A להארקה דרך סיומת של 50 אוהם.

◄ חבר את ערכת ההערכה למחשב Windows® 10 דרך כבל USB. פתח את התוכנה של ערכת ההערכה ל- MAX32007 (ממשק משתמש גרפי – GUI).

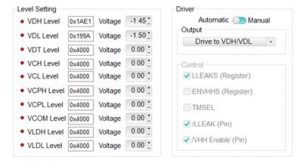

◄ החל את רמות המתח של ממיר DAC ואת הגדרות המעגל הדוחף כפי שמוצג באיור 4. שים לב שערך מתח הפעולה הנמוך ביותר של VDH הוא 1.5 וולט, ערך מתח הפעולה הגבוה ביותר של VDH הוא 4.5 וולט. במקרה זה, הערך של נקודת היסט האפס היא 1.5 וולט.

איור 4. ההגדרה של רמת ממיר DAC של MAX32007 באמצעות התוכנה של מעגל ההערכה. קרדיט: ANALOG DEVICES

◄ קבע VDH = –1.5 וולט ומדוד את הערך של מתח המוצא.

◄ קבע VDH = 4.5 וולט ומדוד את הערך של מתח המוצא.

◄ תיקון שבח = ההפרש בין ערכי המוצא הנמדדים מחולק בהפרש בין הערכים האידיאליים. לדוגמה: (4.501 – (–1.497)) / (4.5 – (–1.5)) = 0.999667.

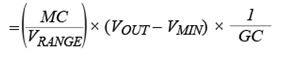

◄ אחרי שתחיל את תיקון השבח,

קוד VDH בכניסת ממיר DAC (עם תיקון שבח)

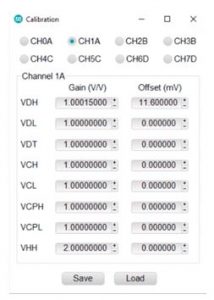

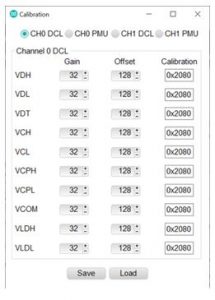

כדי להחיל את תיקון השבח, פתח את התפריטים Menu ß Options ß Calibration (תפריט ß אפשרויות ß כיול), כמוצג באיור 5.

איור 5. תפריט הכיול של ממיר ספרתי לאנלוגי MAX32007. קרדיט: ANALOG DEVICES

איור 6. תיקון שגיאת INL עבור ממיר DAC עם אוגרי תיקון. קרדיט: ANALOG DEVICES

◄ החל VDH = 1.5 וולט (עם קוד תיקון שבח) ומדוד את ערך המתח במוצא.

◄ תיקון היסט = מדוד את ערך המוצא – הערך האידיאלי. לדוגמה, (1.502 – 1.5) = 0.002.

◄ אחרי שתחיל את תיקוני השבח וההיסט,

קוד VDH בכניסת ממיר DAC (עם תיקוני שבח והיסט)

דוגמה 2

נשקול את MAX9979, שהוא DCL כפול עם ממירי DAC משולבים לקביעת רמה ויחידת PMU. להתקן MAX9979 יש ממירי DAC פנימיים עבור ערכי VDH, VDL, VDT, VCH, VCL, VCPH, VCPL, VCOM, VLDH, VLDL, VIN, VIOS, CLAMPHI/ VHH ו- CLAMPLO לקביעת רמה. לממירי DAC אלו יש אוגרים פנימיים לכיול. בדוגמה 1, קודי הכניסה של ממיר DAC עוברים כוונון כדי להקטין את שגיאת INL למינימום. בדוגמה 2, קוד הכניסה של ממיר DAC נותר זהה ואוגרי הכיול משמשים לכיול חוצץ דרגת המוצא כדי להקטיו את שגיאות INL למינימום, כפי שמתואר באיור 6. על מנת לכייל את ממירי DAC, יש להשתמש בתהליך הבא:

◄ הפעל את ערכת ההערכה (EV) של MAX9979 על ידי כך שתעקוב אחר ההוראות בדף הנתונים של ערכת ההערכה.

◄ חבר את מחברי SMB, DATA0A ו- NTRM0A למתח של 1.2 וולט.

◄ חבר את מחברי SMB, NDATA0A ו- TRM0A להארקה דרך סיומת של 50 אוהם.

◄ חבר את ערכת ההערכה למחשב Windows® 10 דרך כבל USB. פתח את התוכנה של ערכת ההערכה ל- MAX9979 (ממשק משתמש גרפי – GUI).

◄ החל את רמות המתח של ממיר DAC ואת הגדרות המעגל הדוחף כפי שמוצג באיור 7. שים לב שערך מתח הפעולה הנמוך ביותר המומלץ של VDH לממיר DAC הוא 1.5 וולט, ערך מתח הפעולה הגבוה ביותר של VDH הוא 4.5 וולט, כאשר הערך של נקודת היסט האפס היא 1.5 וולט.

איור 7. ההגדרה של רמת ממיר DAC של MAX9979 באמצעות התוכנה של מעגל ההערכה. קרדיט: ANALOG DEVICES

◄ החל VDH = –1.45 וולט ומדוד את ערך המתח במוצא.

◄ החל VDH = 6.5 וולט ומדוד את ערך המתח במוצא.

◄ תיקון שבח = ערכי ההפרש בין מתחי המוצא הנמדדים חלקי ההפרש בין ערכים אידיאליים. לדוגמה, (6.501 V – (–1.455 V))/(6.5 V – (–1.45 V)) = 1.0007 V.

◄ אחרי שתחיל את תיקוני השבח וההיסט,

קוד VDH בכניסת ממיר DAC (עם תיקון שבח)

הערה: אפשר להפעיל תיקוני שבח והיסט בתפריט Menu ß Options ß Change ß Calibration (תפריט ß אפשרויות ß שינוי ß כיול), כמוצג באיור 8. המרה של תיקוני שבח והיסט וקודי היסט נתונים בדף הנתונים של MAX9979.

איור 8. הגדרה של אוגר כיול של MAX9979. קרדיט: ANALOG DEVICES