סקירה כללית: התקנים היקפיים על-שבב עם לוגיקה וגמישות משפרים יישומים על ידי הקטנת נפח הקוד, הפחתת צריכת המתח ושיפור ביצועי המערכת, על ידי יישום לוגיקה דיסקרטית ו/או חיבור של ציוד היקפי אחר.

התקני חומרה היקפיים על-שבב ידועים ביכולתם להפחית את צריכת המתח, לשפר את הביצועים, להגדיל את יכולות ההתקן ולצמצם את נפח הקוד. ניתן להשיג את ההתקנים ההיקפיים האלה במבחר “טעמים”, החל ממגברים תפעוליים וממירים אנלוגיים-דיגיטליים משופרים (ADC) וכלה במודולטורים של רוחב דפקים (PWM) וטיימרים אוניברסליים (UTMR). אחד מסוגי ההתקנים ההיקפיים העוצמתיים ביותר הוא זה שניתן ליישם בו לוגיקה דיסקרטית או שניתן לחבר אותו להתקנים היקפיים אחרים. במאמר זה אבחן את ההתקנים ההיקפיים של יציאת Configurable Logic Cell (CLC), יציאת Configurable Custom Logic (CCL), יציאת Event System (EVSYS), ונקודת חיבור Signal Routing (SR) וכיצד ניתן להשתמש בהם להוספת ערך לתכן שלכם.

CLC / CCL

ההתקנים ההיקפיים של Configurable Logic Cell (תא לוגי ניתן-לתצורה, CLC) ושל Configurable Custom Logic (לוגיקה מותאמת-אישית ניתנת-לתצורה, CCL) הוא בצורת טבלאות חיפוש ניתנות-לתכנות (LUT) כאשר כל אחד מהם הוא למעשה שווה-ערך לתא יחיד של FPGA. הפונקציה הלוגית שתצורתה מוגדרת בתוך כל מופע היקפי מוגדרת ב-runtime. ה-CLC/CCL יכולים לפעול באופן בלתי תלוי ב-CPU, דבר המאפשר להם להחליף שבבי לוגיקה דיסקרטית בתכן. בכל הנוגע להבדל בין CLC לבין CCL: יש הבדלים מינוריים ביישום שלהם – ה-CLC הוא ספציפי למיקרו-בקר ®PIC בעוד שה-CCL הוא ספציפי למיקרו-בקר AVR®. הפעולה הבסיסית של כל התקן היקפי היא עדיין זהה.

דיבאונסינג של לחצנים ומתגים

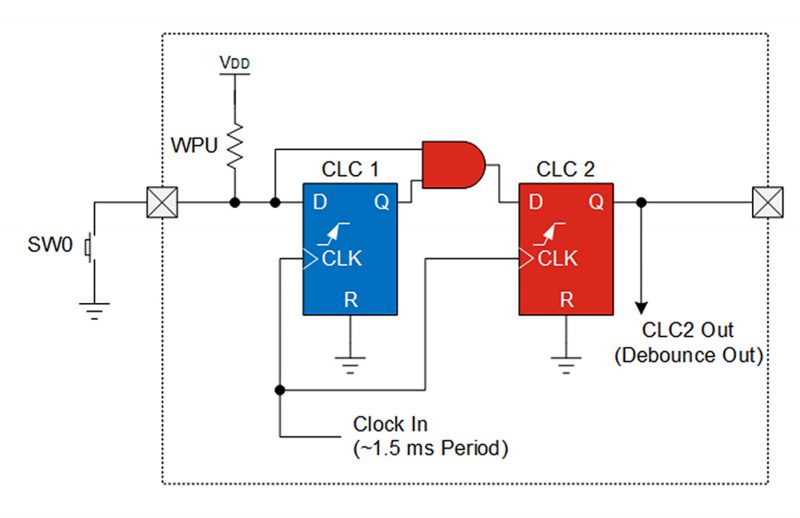

אחת מדוגמאות השימוש הנפוצות ביותר עבור CLC/CCL היא ליישם דיבאונסינג (Debouncing) ברמת-החומרה יחד עם טיימר/מתנד. Application Note 2805 (AN2805) דן בשלוש דרכים ליישום דיבאונסינג תוך שימוש ב-CLCs. מתוך השלישייה הזו, שתי גרסאות ה-CLC הציעו איזון מוצלח בין שימוש במשאבי חומרה לבין ביצועים. קוד המקור של שלוש הגרסאות זמין ב-GitHub.

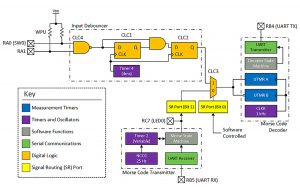

כדי ליישם את הדיבאונסר, אחד מה-CLCs מוגדר כ-D flip-flop כדי לנעול (latching) את הערך מתוך הלחצן או המתג. ה-CLC השני מבצע פעולת AND לוגית על הערך הנעול מהשלב הקודם עם הקלט הישיר, ואז נועל את הערך של התוצאה. מקור השעון של שני ה-flip-flops הוא מקור שעון בתדר נמוך שמפיק טיימר או מתנד על ההתקן. היישום מוצג להלן.

תרשים 1 – CLC עם שני דיבאונסרים

עבור ה-CCLs ב-AVR MCUs, זה אפילו פשוט יותר מזה. ה-CCLs מכילים אופציית סינון קלט שמבצעת למעשה את אותה פעולת סינון דו-מחזורית שיושמה על ה-CLCs. בנוסף, ניתן לבצע קלוקינג של ה-CCLs ממתנד של 1kHz על ההתקן שהוא איטי מספיק כדי לבצע דיבאונסינג.

פענוח ריבועי

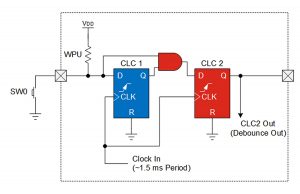

דוגמת שימוש נוספת ב-CLCs הוא ביצוע של פענוח ריבועי (Quadrature decoding). מקודדים ריבועיים תוספתיים (incremental) מפיקים שני גלים ריבועיים שהמופע של אחד מהם מוביל על המופע של השני ב-90 מעלות. מידת הסיבוב נקבעת על ידי מספר צורות הגל, בעוד שהמופע של צורת הגל מציין את הכיוון. התמונה להלן מציגה דוגמה של אות ריבועי מקודד.

תרשים 2 – דוגמה של צורת גל ריבועית

כדי לפענח זאת, ה-CLCs ממירים את צורת הגל הזו לשני אותות פלט המייצגים דפקים עם כיוון השעון ונגד כיוון השעון. שני טיימרים במיקרו-בקר סופרים את מספר הדפקים שהתקבלו. כאשר המיקרו-בקר צריך לדעת את השינוי נטו של המיקום, ניתן לבצע תרגול מתמטי פשוט לגבי הספירות של כל טיימר כדי לקבוע את השינוי נטו מאז הקריאה האחרונה.

מערכת האירוע

מערכת האירוע (Event System, או EVSYS) מתוכננת כך שתבחר אות פלט מהתקן היקפי אחר ותנתב אותו להתקנים היקפיים אחרים פנימיים ביחס למיקרו-בקר. החיבוריות-הצולבת הזו יכולה להתרחש באופן עצמאי מה-CPU, דבר שחוסך הספק במצב שינה או סרק ומשפר את הביצועים. את ה-EVSYS ניתן למצוא רק במיקרו-בקרים מסוג AVR.

נקודת חיבור SR

במיקרו-בקרים מסוג PIC יש התקן היקפי הידוע כנקודת חיבור SR (Signal Routing Port). נקודת חיבור ה-SR היא מבנה הדומה לפלט I/O, אך כזה שהוא פנימי (internalized). ניתן להשתמש בתוכנה כדי להגדיר או למחוק באופן ידני את הביטים בפנים, כמו אוגר פלט I/O סטנדרטי, אך היא גם תומכת באותות פלט היקפיים ובפונקציונליות של אוגר הסטה (shift register).

נקודת חיבור ה-SR גם עובדת היטב עם תכונת ה-Peripheral Pin Select (או PPS) שניתן למצוא אותה גם במיקרו-בקרים מסוג PIC. ה-PPS מעניק למתכנן גמישות בהקצאת I/O בכך שהוא מאפשר להסיט אותות I/O דיגיטליים לפינים שונים במיקרו-בקר. באופן דומה, ה-PPS מאפשר להתקנים היקפיים לבחור “פינים” של נקודת חיבור ה-SR כאותות קלט באופן אינדיווידואלי. כך ניתן לתכנן ולשלוט במכונות מצב-מתקדם באמצעות ההתקן ההיקפי הזה.

בחירת אות על-ההתקן

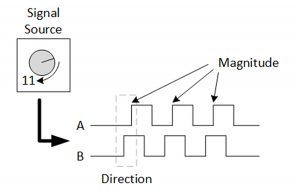

דוגמה אפשרית אחת לשימוש בנקודת חיבור ה-SR וב-CLC היא להשתמש במרבב בחירת אות פנימי (internal signal select multiplexer). ניתן להשתמש בזה לבדיקה-עצמית פנימית או לבחירת אחד מאותות ה-N לצורך עיבוד. כדי ליישם זאת, משתמשים ב-CLC ליצירת מרבב 2:1. אפשר גם להשתמש במרבב 4:1, אך הוא משתמש בשלושה CLC ובשני ביטים מיציאת SR. כדי ליצור את המרבב, משתמשים בביט מיציאת ה-SR כ-select line. היישום הלוגי מוצג להלן.

תרשים 3 – מרבב 2:1 (כפי שהוא מיושם במסגרת CLC לוגי; אותות קלט שאינם בשימוש הם מוסתרים)

יתרון אחד שיש ליישום הזה על פני PPS הוא מהירות וגמישות. ניתן לנעול את ה-PPS כדי למנוע שינויים לא זהירים ב-runtime. בנוסף, ניתן להגדיר ביט config כדי לוודא שניתן לנעול את ה-PPS רק פעם אחת. במקום זאת, הגדרת מרבב CLC מאפשרת לתוכנית לשנות אותות קלט בלי שיהיה צריך לבצע רצף ביטול נעילות בכל פעם מחדש. דוגמת השימוש הזו נמצאת בהדגמת קוד מורס (Morse Code demo) עבור משפחת PIC18F56Q71 של Microchip. ההדגמה יוצרת משדר ומקלט פשוטים של קוד מורס – המרבב משמש לבחירה בין פלט המשדר לבין אות קלט חיצוני לצורך הקליטה.

תרשים 4 – דיאגרמת בלוקים של הדגמת קוד מורס

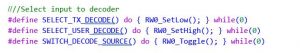

בתוך התוכנית, מגדירים מאקרו של 1 ביט מסוג set/clear/toggle עבור הפינים של נקודת חיבור ה-SR, זאת לצורך קריאות (readability).

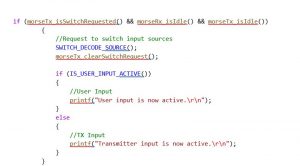

פיסת הקוד להלן אחראית על ניקוי המיתוג בין מקורות הקלט. כאשר המשדר והמקלט הם במצב סרק, והמשתמש שלח ‘#’ למסוף, הוא יבצע מיתוג בין מקורות הקלט.

קוד המקור של תוכנית זו זמין ב-GitHub.

חישוב זוגיות (parity) מואץ ע”י חומרה

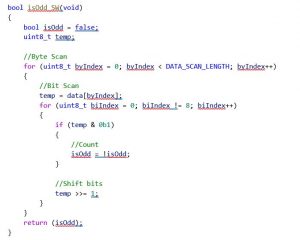

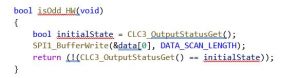

במקרים מסוימים יש צורך להפיק ספרת זוגיות לצורך שידור או תקשורת נתונים. חישוב הזוגיות בתוכנה הוא טריוויאלי, אך איטי יותר לביצוע מאשר בחומרה. להלן מוצגת פונקציה פשוטה.

הערה: דפוס הבדיקה שנבדק מאוחסן גלובלית עבור הדוגמאות הפשוטות האלה.

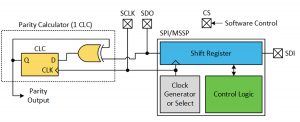

כדי להאיץ את החישוב, ניתן להשתמש בהתקן היקפי מסוג SPI עם CLC לבניית מחשבון זוגיות מבוסס-חומרה. חומרת ה-SPI מכילה אוגר הסטה טורית (serial shift register) לשידור ולקליטה של נתונים. אות הפלט של חומרת ה-SPI (אוגר ההסטה) ניתן להזנה לתוך CLC לצורך הפעלת מחשבון זוגיות שפועל בקצב מהיר יותר משמעותית מאשר גרסת התוכנה.

תרשים 5 – יישום חומרה

יישום זה יכול גם לעשות שימוש מחודש בהתקנים היקפיים קיימים מסוג SPI, ובכך להפחית עוד יותר את עלויות היישום. הסיבה היא שבדרך כלל צריך להצהיר (assert) על קו ה-Chip Select (CS) כדי לתקשר עם התקני SPI אחרים. אך אם לא מצהירים עליו, יש התעלמות מהתקשורת הזו.

כדי לבצע את הגרסה המואצת ע”י חומרה, תחילה עליך ללכוד את הערך הנעול הנוכחי ב-CLC. לאחר מכן יש לשדר את הנתונים שצריך לחשב עבורם זוגיות כאשר ה-CS אינו מוצהר (deasserted). לאחר מכן, עיין בערך החדש הנעול ב-CLC. אם הערך החדש שווה לערך הקודם, זה אומר שנספר מספר זוגי של ‘אחד-ים’. אם הערכים אינם תואמים, זה היה מספר אי-זוגי. התוכנה לחישוב זוגיות אי-זוגית (odd parity) מוצג להלן.

כדי להדגים את יתרון המהירות, יצרנו תוכנית הדגמה קטנה במשפחת המיקרו-בקרים PIC16F18146 של Microchip. אחד הטיימרים הפנימיים, טיימר 1, משמש לספירת מספר מחזורי השעון (FOSC/4) שדרוש לביצוע חישובי הזוגיות באמצעות חומרה ובאמצעות תוכנה. התוצאות מודפסות למסוף טורי לצורך ניתוח. להלן ניתן לעיין בעותק של תוצאות הביצועים של רמות אופטימיזציה שונות של הקומפיילר.

טבלה 1 – הבדלי ביצועים בין יישומי תוכנה וחומרה, רצף של 10 בייטים

| רמת אופטימיזציה | זמן תוכנה | זמן חומרה | הבדל ביצועים (%) |

| רמה 0 (ללא) | 1726 | 552 | +313% |

| רמה 1 | 1371 | 533 | +257% |

| רמה 2 | 1371 | 533 | +257% |

| רמה 3 (מהירות) | 1019 | 465 | +219% |

| רמה S (גודל) | 1019 | 465 | +219% |

שיפור הביצועים המוצג בדוגמה זו תלוי במהירויות השעון של המיקרו-בקר ושל ההתקן ההיקפי מסוג SPI. קוד המקור של תוכנית זו זמין ב-GitHub.

מחשבות לסיכום

התקני חומרה הם תכונה חשובה במערכות מוטמעות. מיקרו-בקרים העושים בהם שימוש יכולים להפוך לחזקים יותר, יעילים יותר ובעלי יכולות גבוהות יותר. התקנים היקפיים עם לוגיקה וגמישות הם כלים עוצמתיים במיוחד לטיפול במשימות פשוטות כגון דיבאונסינג (debouncing) או פענוח ריבועי (quadrature decoding). שימוש יצירתי בהתקנים היקפיים משפר את התכנונים ומרחיב את הגבולות של מה שניתן לבצע על מיקרו-בקרים.