תכנון המבוא, או הקצה הסופי (front end), של כל ממיר אנלוגי לדיגיטלי () איכותי, במיוחד ADC דוגם-RF, הוא קריטי כדי להשיג את הביצועים ברמת המערכת הרצויים. בהרבה מקרים, ה-ADC דוגם-ה-RF מעביר לדיגיטלי רוחב-פס של אות בעל מאות מגה-הרץ.

הקצה הסופי יכול להיות אקטיבי (על ידי שימוש במגבר) או פסיבי (ע”י שימוש בשנאים או בלונים) בהתאם לדרישות המערכת. בכל מקרה, יש לבחור בקפידה את הרכיבים על מנת לספק ביצועי ADC משופרים בתחום התדרים בעלי עניין.

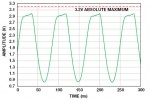

ADCs דוגמי-RF מיוצרים תוך שימוש בטכנולוגיה של תהליך CMOS תת-מיקרוני עמוקה, והפיזיקה של המוליך-למחצה אומרת לנו שגיאומטריות טרנזיסטור קטנות יותר תומכות במתחים מרביים נמוכים יותר. לכן, גיליון הנתונים מציין את המתחים המרביים המוחלטים שאין לעלות עליהם בשל שיקולי אמינות. השוואה בין גיליונות נתונים של התקנים ישנים יותר עם ה-ADCs דוגמי-ה-RF החדישים מוכיחה את הפחתת מתח זו.

ביישומי מקלטים בהם ה-ADC הופך לדיגיטלי את אות המבוא, מתכנני המערכת צריכים לשים לב היטב למתח המבוא המרבי המוחלט. פרמטר זה משפיע ישירות על ביצועי ה-ADC והאמינות במרוצת החיים. ADC לא אמין יהפוך את כל מערכת הרדיו לחסרת שימוש, והעלות של החלפתה עשויה להיות משמעותית.

כדי לבטל את הסיכונים ממאמץ של מתח-יתר, ADCs דוגמי-RF כוללים מעגלים המגלים ספים גבוהים, המאפשרים למקלט לפצות על-ידי כוונון השבח בעזרת לולאת בקרת שבח אוטומטית (automatic gain-control). עם ADC בעל חפיפה (pipelined), הכמיסה האינהרנטית הכרוכה בארכיטקטורה עשויה לחשוף בקצרה את המבוא לרמה גבוהה, ולהזיק בכוח למבואות ה-ADC. מאמר זה דן בשיטה פשוטה שעשויה להגדיל את לולאת ה-AGC כדי להגן על ה-ADC.

ארכיטקטורות מבוא

ADCs דוגמי-RF מיושמים בתכנונים שונים אחדים, כאשר המקובל ביותר הוא ארכיטקטורת החפיפה, אשר מדרגת דרגות אחדות כדי להמיר את האות האנלוגי לדיגיטלי. הדרגה הראשונה, שהיא הקריטית ביותר, יכולה להיות חצוצה (buffered) או לא-חצוצה. הבחירה של השימוש בהן תלויה בדרישות התכנון ומטרות הביצועים. לדוגמה, ADC חצוץ מציע לרוב SFDR טוב יותר לאורך התדר אך צורך יותר הספק מאשר ADC לא-חצוץ.

תכנון הקצה הסופי ישתנה גם לפי זה

שה-ADC הוא חצוץ או לא. הנגד הטורי הנוסף הדרוש ב-ADCs לא-חצוצים כדי לטפל בתחזיר (kickback) המטען במבוא עשוי לשפר גם את ביצועי ה-SFDR. איור 1 ואיור 2 מראים מעגלי מבוא שווי-ערך מפושטים של ה-ADCs דוגמי ה-RF AD9625 הלא-חצוץ וה-AD9680 החצוץ. רק המבואות המוארקים מוצגים לשם פשטות.

ללא תלות בארכיטקטורה, המתח המרבי המוחלט שניתן לקבל במבואות ה-ADC נשלט על-ידי המתחים שה-MOSFETs יכולים לשאת. המבוא החצוץ הוא יותר מורכב וצורך יותר הספק מאשר המבוא הלא-חצוץ. ADCs משתמשים בסוגים שונים אחדים של חוצצים, כאשר המקובל ביותר הוא העוקב פולט.

מנגנוני כשל

מנגנון הכשל יהיה שונה עבור ADCs חצוצים ולא-חצוצים, אך כשל קורה לרוב כאשר עוברים על המתח שער-מקור המרבי המותר (VGS) או המתח קולט-מקור (VDS). מתחים אלה מוצגים באיור 3.

לדוגמה, אם VDS עולה מעל המתח המרבי המותר, הוא גורם כשל פריצה של ה-VDS, הקורה לרוב כאשר ה-MOSFET נמצא במצד off ומחברים מתח מעל המותר לקולט ביחס למקור. אם ה-VGS עולה על המתח המרבי המותר, הוא גורם לנקב של VGS, הידוע גם ככשל תחמוצת. דבר זה קורה לרוב כאשר MOSFET הוא ב-on ומתח מופרז מחובר לשער ביחס למקור.

מנגנון הכשל ב-ADC לא-חצוץ

איור 4 מראה מבוא של ADC לא-חצוץ.תהליך הדגימה מבוקר על-ידי אותות השעון Φ ו-Φ-, שהם האות דגום-ושמור עבור ה-MOSFET M1 ואות האיפוס עבור ה-MOSFET M2. כאשר M1 הוא on, M2 הוא off, והקבל CSW עוקב אחר האות (במוד דגום או עקוב). כאשר M1 הוא off, M2 מופעל אחרי שהמשווים ב-MDAC לקחו החלטה, ואיפסו את הקבל CSW. דבר זה מכין את קבל הדגימה עבור הדגימה הבאה במהלך שלב הדגימה. מעגל זה פועל לרוב כמו מכונה משומנת היטב.

אולם, מבואות במתח גבוה חושפים את המעגל למאמצים החורגים מגבול מתח הקולט-מקור עבור M2. כאשר מבוא במתח גבוה מודגם (M1 הוא , M2 הוא ), M2 נחשף ל-VDS גדול. M2 הוא off בשביל פחות מחצי מחזור של שעון הדגימה, אך אף חשיפת תופעת המעבר עשויה לקלקל את אמינות המעגל ולהפוך את ה-ADC ללא שימושי במשך הזמן. M1 נחשף ל-VDS גדול במוד של איפוס (M1 הוא , M2 הוא )כאשר אות המבוא מופיע בקולט שלו.

מנגנון הכשל ב-ADC חצוץ

איור 5 מראה מבוא ADC חצוץ. אותה הסכימה של השעון תקפה עבור אותות דגימה ואיפוס. ללא קשר למופע, כאשר השער של החוצץ M3 נחשף למבוא במתח גבוה, הוא מאמץ את המעגל היוצר את הזרמים I1 ו-I2. מקור הזרם I1 ממומש בעזרת טרנזיסטור PMOS, בעוד ה-I2 ממומש על-ידי טרנזיסטור NMOS. מתח גבוה בשער של M3 יוצר VDS מוגזם בשני הMOSFETs- I1 ו-I2. בנוסף, מתח גבוה על השער של M3 עשוי ליצור כשל בתחמוצת.

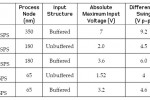

מנגנוני הכשל הם שונים עבור ADCs חצוצים ולא-חצוצים, כך שמתח המבוא המרבי המוחלט גם שונה כמתואר בטבלה 1.

הגנה על מבוא ה-ADC תוך שימוש בדיודת TVS

ניתן להגן על מבואות ADC נגד מתחים גבוהים בדרכים שונות. ל-ADCs אחדים, כולל ADCs דוגמי-RF במיוחד, יש מעגלים מובנים המגלים ומדווחים כאשר הספים המתוכנתים נחצו. למוצא מהיר-גילוי זה יש כמיסות מסוימת, כמתואר בגיליון הנתונים, כך שהוא משאיר את מבוא ה-ADC חשוף לתקופת זמן קצרה.

ניתן להגביל את המתח העודף בעזרת דיודות מייצבות תופעות מעבר (transient voltage-stabilizer) אולם הן מסכנות את ביצועי ה-ADC במהלך פעולה רגילה. איור 6 מראה מעגל המשתמש בדיודות TVS כדי להגן בפני תנאי מתח-יתר.

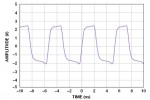

למרות שדיודות ה-TVS מגנות על מבואות ה-ADC על-ידי ריתוק של המתח העודף, הן פוגעות בצורה חמורה בביצועים ההרמוניים. איור 7 מראה FFT של ADC לא-חצוץ של 14-ביט, 250 MSPS, עם מבוא של 30 מגה-הרץ, ~1dBFS עם וללא דיודת TVS בקצה הסופי.

דיודות ה-TVS פוגעות במיוחד בהרמוניות האי-זוגיות מאחר שהן פועלות בתור דיודות בעלות משוב-הפוך כאשר הן לא מרתקות. לדיודת PN זו יש קיבול צומת, CJO הפועל עם זרם התחזיר הלא-ליניארי המיוצר על-ידי פעולת המיתוג בתוך ה-ADC כדי ליצור מתח המתערבב עם אות המבוא האנלוגי. האות המעורב מודגם בתוך ה-ADC ויוצר הרמוניה מסדר שלישי משמעותית. גרף במישור הזמן של תנאי מתח-היתר (איור 8) מראה את פעולת הקיטום של דיודות ה-TVS. דבר זה איננו אומר שדיודת ה-TVS איננה מתאימה לשם הגנת מבוא ה-ADC, אלא רק שיש להתחשב בזהירות במפרטי הדיודה בכדי לקבל את הביצועים הדרושים. דרוש מבט יותר מעמיק בבחירת סוג הדיודה והפרמטרים שלה.

הגנה של מבואות ADC דוגמי-RF תוך שימוש בדיודות Schottky

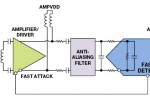

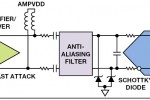

בשעה שרוחבי-הפס וקצבי הדגימה הגיעו לתחום ה-גיגה-הרץ וה-GSPS, ADCs דוגמי-RF מפשטים את תכנוני מקלט הרדיו מאחר שהם אינם דורשים כל כך הרבה דרגות עירוב בחזית ה-ADC, אך הדבר משאיר את מבואות ה-ADC פגיעים למאמצי מתח-היתר. איור 9 מראה תכנון קצה סופי מוזן על-ידי מגבר אופייני עבור ADC דוגם-RF. לדור החדש של מגברים מתוכנן במיוחד כדי למשק עם ADCs אלה יש מבוא בעל תקיפה מהירה שניתן לעצב דרך הממשק ההיקפי הטורי (serial peripheral interface) כדי להפחית את המוצאים לשבח שנקבע מראש. פין ההתקף-המהיר ניתן לעיצוב כדי לענות למוצא בעל הגילוי-המהיר מה-ADC הדוגם-RF. ה-ADA4961 היא דוגמה של הדור החדש של מגברים בעלי התכונה של תקופה מהירה. ה-AD9680 ו-AD9625 הן דוגמאות של ADCs דוגמי RF בעלי התכונה של גילוי מהיר.

הטופולוגיה של איור 9 טובה כל עוד מתחי המבוא נמצאים בתוך התחום. אם, לדוגמה, נתיב מקלט זה נחשף למכה פתאומית של מתח גבוה במבוא, המוצאים עשויים לעלות למתח של פס ההספק של המגבר (5 וולט, במקרה זה). דבר זה מהווה ניד ענקי החורג מהמתח הנקבע למרב מוחלט במבואות ה-ADC. לגילוי המהיר יש במיסות מסוימת (28 מחזורי שעון או 28 ננו-שניות עבור ה-AD9680-1000), כך שבזמן שמוצא הלוגיקה של הגילוי המהיר אומר שעל המגבר ליזום תקיפה מהירה, ה-ADC כבר נחשף למתח הגבוה למשך מחזורי שעון אחדים. דבר זה עשוי לפגוע באמינות ה-ADC, כך שתכנוני מערכת שאינם יכולים לעמוד בפני סיכון זה יזדקקו למוד משני של הגנה. דיודת Schottky בעלת פעולה מהירה עם קיבול התקן ופרזיטי מאוד נמוך היא שימושית במצבים אלה. פרמטרים עיקריים להגדרת הדיודה ניתן למצוא בגיליון הנתונים.

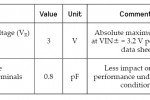

מתח כשל הפוך (VBR) – מתח המבוא המרבי בפיני המבוא של ה-AD9680 – הוא כ-3.2 וולט יחסית ל-AGND, כך שמתח כשל הפוך של 3 וולט נבחר עבור הדיודה.

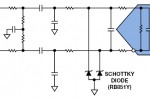

קיבול הצומת (CJ0) – קיבול הדיודה צריך להיות נמוך ככל האפשר כדי להבטיח שהדיודה אינה משפיעה על ביצועי ה-ac של ה- (SNR/SFDR) במהלך פעולה רגילה. איור 10 מראה קצה סופי פסיבי עם דיודת Schottky מחוברת בחזית ה-ADC. הקצה הסופי הפסיבי מקל על ההוכחה שדיודת Schottky יכולה להגן על מבואות ה-ADC מבלי לסכן את ביצועי ה-ac.

ה-ADC דוגם-RF נבדק לתדרי מבוא של עד 2 גיגה-הרץ ולכן נבחרה דיודת (Schottky RB851Y). טבלה 2 מראה את פרמטרי המפתח של ה-RB851Y העושים אותה מתאימה ליישום. נערכו בדיקות כדי להראות שהדיודות מנעו את מבואות ה-ADC מלעבור את ערך המתח המרבי של 3.2 וולט ביחס ל-AGND. איור 11 מראה מבור מוארק) פין VIN+ של ה-ADC) נחשף למתח גבוה ב-185 מגה-הרץ. דיודת Schottky מרתקת את המתח ל-3.0 וולט ביחס ל-AGND, ומונעת בכך את ה-ADC מלהגיע לגבול של 3.2 וולט. איור 12 מראה אות הפרשי במבוא של ה-AD9680 הקטום על-ידי דיודות Schottky.

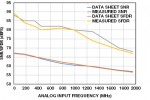

בהמשך, מדדנו את הביצועים במהלך פעולה רגילה. ה-AD9680 נבדק על-פי המלצות גיליון הנתונים, אך המבואות שונו כמתואר באיור 10.

תדר המבוא האנלוגי שונה מ-10 מגה-הרץ ל-2 גיגה-הרץ. הערך הנמוך ביותר של CJ0 לא צריך להשפיע על ביצועי ה-SNR ו-SFDR של ה-ADC.

דיודות ה-Schottky אינן משפיעות כלל על ה-SNR, אולם ה-SFDR סוטה מהערך המצופה בתדרים מסוימים, כמתואר באיור 13. דבר זה עשוי לקרות בשל אי-תאום באות ההפרשי או תחזיר מה-ADC. כרטיס ההערכה מתוכנן לרוחב פס רחב, מ-dc ל-2 גיגה-הרץ, כך שבעוד הוא מבצע עבודה טובה לאורך כל התחום, רכיבים אחדים עשויים לפעול הדדית עם דיודות ה-Schottky בתדרים מסוימים.

רוב היישומים אינם משתמשים בכל תחום ה-2 גיגה-הרץ, כך שאפשר לכוון את הקצה הסופי לרוחב-הפס הדרוש ובעל העניין על-ידי שינוי המבוא עבור הגנת מתח-היתר. בחירה זהירה של דיודת Schottky יכולה להגן על מבואות ה-ADC, ולאפשר למתכנן המערכת לממש מעגל קצה סופי מוזן על-ידי מגבר תוך שימוש בתכונות התקיפה-המהירה והגילוי-המהיר, כמתואר באיור 14.

סיכום

מאמר זה הציג את השימוש בדיודת Schottky כדי להגן על המבואות של ADC דוגם-RF כנגד מאמצי מתח-יתר. בחינה זהירה של גיליון הנתונים של הדיודה היא חיונית. דרושה תכנית ליישם את המעגל הזה כדי להשיג ביצועים מיטביים בתחום העניין. המוצא מהיר-הגילוי של ADC דוגם-RF יכול לתקשר עם המבוא מהיר-התקיפה של המגברים האחרונים כדי להסדיר את לולאת בקרת השבח האוטומטית.

- איור 1. מעגל שווה-ערך של מבוא ADC דוגם- RF לא חצוץ

- איור 2. מעגל שווה-ערך של ADC דוגם RF חצוץ

- איור 3. מתחים קריטיים עבור טרנזיסטור MOS

- איור 4. מוד הכשל במבוא לא-חצוץ של ADC

- איור 5. מוד הכשל במבוא חצוץ של ADC.

- איור 6. מעגל קצה סופי ADC עם הגנת דיודת TVS.

- איור 7. השוואת FFT של מעגל קצה סופי של ADC עם וללא הגנת דיודת TVS.

- איור 8. אות קטום בשל הגנת דיודת ה-TVS במעגל הקצה הסופי.

- איור 9. מגבר בעל תקיפה מהירה המזין ADC דוגם-RF העל גילוי מהיר.

- איור 10. מעגל קצה סופי המראה ADC דוגם-RF ודיודת Schottky.

- איור 11. מבוא ADC מוארק הקטום על-ידי דיודת Schottky.

- איור 12. מבואות הפרשיים של AD9680 הקטומים על-ידי דיודות Schottky.

- איור 13. SNR/SFDR כנגד תדר המבוא האנלוגי עבור AD9680 עם הגנה של דיודת Schottky.

- איור 14. ADA4961 המזין את ה-AD9680 תוך הצגת ה-ADC הדוגם-RF ודיודות Schottky.

- טבלה 1. מפרטי מרב מוחלטים עבור ADCs חצוצים ולא חצוצים

- טבלה 2. פרמטרי-מפתח עבור דיודת Schottky המשמשת כדי להגן על מבואות ה-ADC דוגם RF

סימוכין

Castera, Jim and Rob Reeder. “Wideband A/D Converter FrontEnd Design Considerations II: Amplifier or Transformer Drive for the ADC?” Analog Dialogue, Volume 41, Number 1, 2007.

Das, Dave Roy. “Techniques for Low Distortion Buffering of High-Speed Switched Capacitor ADCs.” Massachusetts Institute of Technology, 1997.

Kester, Walt. The Data Conversion Handbook. Analog Devices, Inc., 2004.

MT-228: High Speed ADC Analog Input Interface Considerations.

Reeder, Rob. “Kicking Back at High-Speed, Unbuffered ADCs.” Electronic Design, 2011.

Reeder, Rob. “Test High-Speed ADCs for Analog-Input Phase Imbalance.” UBM Electronics, 2011.

Shedge, Dnyandeo, Devendra Itole, Milind Gajare, and Prakash Wani. “Analysis and Design of CMOS Source Followers and Super Source Follower.” ACEEE.