חיישן התמונה הוא אולי החלק החשוב ביותר של תהליך עיבוד תמונת הסטילס או הווידיאו במצלמת סטילס או וידיאו דיגיטלית. בלי חיישן, אין אות של תמונה לעבד. בנוסף ולרוע המזל, אין תיקנון (סטנדרטיזציה) בחיישנים. הם נוטים לשוני בשיטות המשמשות לדברים הבאים:

א. האופן שבו הם ממירים אור נראה או אינפרא אדום לאותות אלקטרוניים. ספציפית, השיטה המשמשת לקידוד ולפעמים לדחיסה של האות לפני שהוא יוצא מהשבב.

ב. האופן שבו צריך לתכנת רגיסטרים בתוך החיישנים כדי לכוונן פרמטרים כמו הגבר, זמן חשיפה, מצבי חיישן (לדוגמה ליניארי, HDR), קואורדינטות התמונה של החיישן וכדומה.

ג. האופן שבו מיושמות בהם פונקציות מיוחדות כמו טווח דינמי גבוה (HDR) או טווח דינמי רחב (WDR), לדוגמה באמצעות חיישנים מרובים באותו מארז, חשיפות מרובות עבור אותה מסגרת תמונה וכיוצא בזה.

ד. הממשקים שיצרני החיישנים מיישמים כדי להוציא את אותות התמונה האלקטרוניים האלה מהחיישן אל לוגיקת העיבוד שבהמשך השרשרת.

FPGA מספקים פלטפורמת לוגיקה מיתכנתת משתלמת ובגודל פיזי קטן מאוד כדי להמיר בקלות אותות מממשקים שונים של חיישני תמונה לאותות דיגיטליים שמתאימים לעיבוד על ידי הלוגיקה שבהמשך השרשרת. FPGA מספקים מנגנון משתלם כדי להתאים למגוון רחב של שיטות לקידוד אותות, שיטות לניהול רגיסטרים, התאמת מנגנוני HDR וממשק עם החיישנים, המאפשר תמיכה ניתנת לתכנות בסוגים שונים של חיישנים.

טכנולוגיות של חיישני תמונה

חיישני תמונה מתחלקים לשני סוגים כלליים, לפי הטכנולוגיה הבסיסית המשמשת להמרת אור נראה לאותות חשמליים. יש חיישני CCD (התקן צמוד מטענים) וחיישני CMOS (מוליך למחצה משלים). מאמר זה מתמקד אך ורק בממשקים של חיישני CMOS.

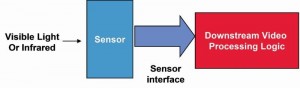

היישום הטיפוסי של חיישן תמונה בשרשרת עיבוד וידיאו הוא כמוצג באיור 1.

יש כיום מספר יצרנים חשובים של חיישני תמונה – ביניהם Aptina, OmniVision Technologies, Sony, Samsung, Panasonic, Toshiba ואטלסנס.

כפי שנאמר קודם לכן, יצרני חיישנים משתמשים מגוון של ממשקים כדי להוציא את אותות התמונה מהשבב שלהם לעיבוד בלוגיקה שבהמשך השרשרת. זה לגמרי נפוץ שאותו יצרן של חיישני תמונה משתמש בממשקים שונים, על בסיס כמות הנתונים שצריך להוציא מהשבב. חיישנים מודרניים עם רזולוציה של מגה פיקסלים, למשל, צריכים להעביר החוצה יותר נתונים בפרק זמן נתון מאשר חיישן עם רזולוציה מסוג VGA בלבד. דרישות כמו טווח דינמי גבוה (HDR) מגדילות אף הן את כמות הנתונים שצריך לקרוא מחיישן התמונה לכל מסגרת תמונה, ואילו מספר המסגרות שצריך להוציא משבב החיישן בפרק זמן נתון, כדי לתמוך בווידיאו חלק יותר, באיכות גבוהה ועם השהיה קצרה, משפיע אף הוא על בחירת הממשק של החיישן.

ההתפתחות הממשקים של חיישני התמונה

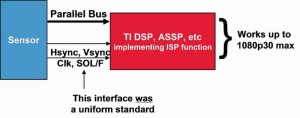

עד עכשיו, כל החיישנים התחברו לממשק LVCMOS מקבילי, כפי שמוצג באיור 2. הרזולוציות וקצבי המסגרות של החיישנים גדלו עכשיו עד כדי כך שממשק ה-CMOS המקבילי שהיה דומיננטי בעבר כבר לא מסוגל לטפל בדרישות קצב ההעברה.

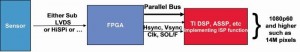

כשהצורך במהירויות גבוהות יותר גדל מאוד בגלל הופעתם של חיישני מגה פיקסלים, HDR והצורך לתמוך בקצבי רענון גבוהים יותר, חיישנים חדשים ומהירים יותר משתמשים בממשקים שונים כדי להתגבר על המגבלות של LVCMOS מקבילי. לדוגמה, סוני ופנסוניק משתמשות בממשקים SUB-LVDS, ו-OmniVision משתמשת ב-MIPI או LVDS טורי. כדוגמה נוספת, Aptina Imaging, כדי לתמוך בצרכים של קצב ההעברה הגבוה יותר, הציגה את הממשק הטורי המהיר שנקרא HiSPi (ממשק פיקסל טורי מהיר). הממשק HiSPi יכול להפעיל בין אחד לארבעה קווי נתונים, בתוספת קו שעון אחד. כל אחד מהאותות הוא דיפרנציאל SUB-LVDS, הממורכז במתח משותף של 0.9V. כל קו יכול להעביר עד 700Mbps.

איור 1. יישום טיפוסי של חיישן תמונה בשרשרת עיבוד וידיאו

איור 2. ממשק LVCMOS מקבילי של חיישן תמונה

הצורך בגישור בין ממשקי חיישנים HiSPi למקביליים

הריבוי של ממשקי חיישנים מהווה בעיה ליצרנים של לוגיקת עיבוד הווידיאו המתוקננת בהמשך השרשרת, משום שקשה לתמוך בממשקי חיישנים שונים רבים ב-ASSP.

רוב התקני ה-ISP (עיבוד אותות תמונה) תומכים בממשקי חיישני ה-CMOS המקביליים המסורתיים, אבל בדרך כלל לא תומכים בממשקים טוריים מהירים. רבים מהממשקים המקביליים של ISP יכולים לפעול הרבה יותר מהר מהממשק המקבילי של החיישן. אולם, בגלל שהחיישנים עברו לממשקים טוריים שונים, התקני ה-ISP צריכים לוגיקה שתתרגם לממשק מקבילי. נחוץ לכן התקן גישור FPGA כדי להמיר את הנתונים הטוריים המהירים לפורמט מקבילי. FPGA פותרים את בעיית ההתממשקות לחיישנים טוריים מהירים עבור היצרנים של ASSP שמעבדים אותות וידיאו, שיש להם קו קיים של מוצרים שתומכים בממשקי חיישני CMOS מהירים יותר. FPGA מאפשרים גישור ניתן לתכנות פשוט ומשתלם בין חיישנים מהירים ו-ASSP מסורתיים שמעבדים אותות תמונה. הרעיון מוצג באיור 3.

איור 3. גשר ניתן לתכנות בין חיישני תמונה מהירים ו-ASSP

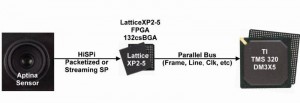

איור 4. גשר ממשקים טורי למקבילי בין Aptina HiSPi ל-TI DM3X5

דוגמא לתכנון של גשר מבוסס FPGA לחיישן טורי

כדוגמה מהעולם האמיתי, ה-FPGA הלא נדיף LatticeXP2-5 מספק פתרון יעיל ומשתלם לגישור בין הממשק הטורי HiSPi של Aptina Imaging ובין הממשק המקבילי TI DSP, כמוצג באיור 4.

תכנון דוגמא הזה מתמשק אל חיישן של Aptina באמצעות ממשק טורי HiSPi בצד הקלט ובאמצעות TI TMS320DM3X5 בצד הפלט. סביבת אבולוציה בדקה את חיישני Aptina A-1000 מהסוגים MT9M034/MTM024 ו-MT9J003. תכנון דוגמא תומך בפורמטי Packeired&streaming: בין קו אחד לארבעה המעבירים עד 700Mbps בכל קו. הוא גם מדמה פלט של חיישן מקבילי, עם רוחבי אפיק פלט של 8, 10, 12, 14 או 16 סיביות. אפשר להגדיר את הממשק המקבילי לרמות LVCMOS של 1.8V, 2.5V או 3.3V. תרשים מלבנים של תכנון דוגמא מוצג באיור 5.

איור 5. תרשים מלבנים של גשר ממשקים בין Aptina HiSPi ל-TI DM385

אתגרי FPGA בגישור ממשקי חיישנים

האתגר בהפעלת רכיב לוגיקה מיתכנת כגשר בין חיישני תמונה ו-ASSP הוא משולש. ראשית, ה-FPGA חייב לספק תמיכה חשמלית לאותות של הממשק. שנית, מנגנון הלוגיקה של I/O GEAR של ה-FPGA צריך להיות מספיק כדי לתמוך בממשקים המהירים של חיישני התמונה. שלישית, הגודל הפיסי של ה-FPGA חייב להיות מאוד קטן ומשתלם כדי שיתאים לדרישות המקום הצר שבמצלמות הווידיאו המודרניות.

משפחת ה-FPGA הלא נדיפים LatticeXP2,עם תמיכה מוכחת ומתועדת ב-SUB-LVDS, עונה על הדרישות החשמליות של גישור חיישני תמונה. ה-PLL המוכללים, שעוני הקצה הייעודיים ומנגנון הלוגיקה של I/O GEAR מטפלים בממשק החיישנים הטורי המהיר. Lattice XP2 מספק גודל פיזי משתלם, קטן עד כדי 8mm x 8mm. בנוסף, בגלל שאינה נדיפה, משפחת ההתקנים LatticeXP2 לא מצריכה PROM אתחול חיצוני, וזה חוסך עוד מקום על הלוח והופך אותם לפלטפורמה מיתכנתת אטרקטיבית לממשקי חיישנים. הזמינות של IP של עיבוד אותות תמונה (ISP) מאפשרת גם להתקני LatticeXP2 גדולים יותר להציע יכולות כמו ליניאריזציה של נתוני החיישן, תכנות הרגיסטרים של החיישן, de-Bayering, תיקון פיקסלים פגומים, תיקון גאמא ו-HDR פשוט עד 24 סיביות לכל ערוץ צבע.