מאת: אריק וינשטיין. לאחר פיתוח במשך 5 שנים והשקעה של מאות שנות אדם השיקה ענקית ה-FPGA את סביבת הפיתוח החדשה, ה-Vivado Design Suite. בכנס מפתחים שערכה החברה הוצגה סביבת הפיתוח החדשה כמו גם סדרה-7 של רכיבי ה-FPGA ומעבדי ה-ZYNQ7000.

מאת: אריק וינשטיין. לאחר פיתוח במשך 5 שנים והשקעה של מאות שנות אדם השיקה ענקית ה-FPGA את סביבת הפיתוח החדשה, ה-Vivado Design Suite. בכנס מפתחים שערכה החברה הוצגה סביבת הפיתוח החדשה כמו גם סדרה-7 של רכיבי ה-FPGA ומעבדי ה-ZYNQ7000.

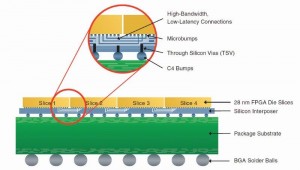

טכנולוגיית-Stacked Silicon Interconnect

ג’יילס פקהאם, מנהל השיווק של אזור EMEA ב-Xilinx: “טכנולוגיית ייצור התלת ממדית (3D) בייצור השבבים מעמידה עדיין אתגרים בפני המפתחים במיוחד בתחום פיזור ההספק. בסדרה 7 של רכיבי FPGA מציגה פתרון ביניים והוא טכנולוגיית ה-Silicon Inter Connect) SSI) שניתן לראותה כ-2.5D. בעזרת טכנולוגיית ה-SSI ניתן ליצור multi-chip עם עד 2 מיליון תאים לוגיים בתוך אריזה אחת עם מאפיינים של שבב יחיד תוך ניהול הספק יעיל“.

בטכנולוגיית ה-SSI משלבים עד ארבע פיסות FPGA מעל שיכבה נוספת של Silicon Interposer מעל למצע האריזה (ציור 1), ובאמצעותה נעשית החיבוריות (Interconnect) בין הפיסות. סידור זה של ארבע פיסות FPGA, שכל אחת מהם יכולה להכיל עד 500 אלף תאים לוגיים, מאפשר להגיע ל-2 מיליון תאים ברכיב אחד. מימוש רכיבים בגודל הזה באמצעות פיסת FPGA יחידה ללא טכנולוגיית ה-SSI היה מוביל ל-yield נמוך מאוד. השימוש בטכנולוגית ה-SSI מבטל את הצורך לדחוף סיגנלי I/O ע”י חוצצים, דבר המביא לחסכון בהספק כמו גם להקטנת ההשהיות. בחברה מציינים כי הקטנת הספק ה-I/O ביחד עם מערכת מתוחכמת לניהול סיגנלים ברכיב מורידה את ההספק הדינמי בצורה משמעותית. יתרון נוסף שמביאה ה-SSI הוא היכולת לשלב טכנולוגיית mixed-signal ברכיב ומימוש תקשורת טורית (SerDes) של 28Gb.

ג’יילס פקהאם: ”סידרה-7 מגדילה מאד את היכולת המסחרית של לקוחותינו לייצר רכיבים מתקדמים“

VivadoTM Design Suite

ה-Vivado היא סביבת פיתוח חדשה שפותחה לתמיכה ברכיבי סדרה 7 של החברה כולל ה-ZYNQ-7000 וכן בדורות הבאים של רכיבי ה-FPGA. בסביבה החדשה הושקעו למעלה מ-500 שנות אדם והיא מתמקדת בתכנון ברמה מערכתית ו-IP להתקנים “מתוכנתים לגמרי” (All-Programmable).

ג’יילס פקהאם: ”עברו הימים שבהם רכיבים מתכנתים הכילו אלפי תאים לוגיים והיו פשוטים יחסית- היום אנו מדברים על מערכות מתוכנתות. סביבת הפיתוח החדשה תוכננה ground-up ככלי פיתוח מערכתי ומאפשרת פיתוח מערכת על FPGA וכן מאיצה את תהליך היישום (implementation). לפיתוח ברמה מערכתית יש דרישות מורכבות: היכולת לעשות שימוש חוזר בתיכנון ו-IP כדי להגן על השקעה בפיתוח, יכולת לשלב IP ממקורות שונים ובשפות שונות כמו RTL או SystemC, שילוב בלוקים פונקציונליים מורכבים כמו DSP, מעבדים ולוגיקה ולהיות מסוגלים לאמת את התכנון ברמת בלוקים וברמה מערכתית. המתכננים צריכים להתמודד גם אתגרים וצווארי בקבוק בשלב היישום של תכנון ברמה מערכתי: תהליך ה-Place & Route, היכולות לעמוד בדרישות ביצועי זמן והספק. ה-Vivado מאפשר האצת תהליכי התכנון והמימוש של המערכת פי-4 ביחס לכלים הקודמים וגם למתחרינו”

ה-Vivado Design Suite מספקת סביבת תכנון משולבת במיוחד עם דור חדש לגמרי של כלים ברמת המערכת עד המעגל המשולב, שכולם מושתתים על היסודות של שימוש במודל נתונים משותף וסביבת ניפוי שגיאות משותפת לכל אורך תהליך היישום. בין הכלים ותכונות עיקריות ניתן למנות:

Vivado HLS: כלי High Level Synthesis המאפשר לקבל בלוקים אלגוריתמיים בשפות כמו C ,C++ או SystemC ולהמיר אותם לשפות -RTL . ה-HLS הוא הכלי הראשון של יצרן FPGA המאפשר סינתזה משפות גבוהות.

Vivado Simulator: סימולטור חדש לגמרי עם אפשרות להאצת סימולציה בחומרה (h/w co-simulation). בבדיקות שנעשו זמני הסימולציה קוצרו פי-3 מול הדור הקודם.

סינתזה ברמת RTL לפי Synopsys Design Constraints עם ביצועים הטובים פי-3 ביחס לדור הקודם.

מנוע Place & Route מתקדם ביותר עם שיפור עד פי-4 בביצועים תוך שמירה על דטרמיניסטיות בזמני ריצה.

Intelligent Clock Gating: יכולת להקטין הספק דינמי על ידי מיסוך שעונים בחלקים שהם לא פעילים.

תמיכה בתקן IEEE P1735 לאבטחת IPs

כדי להתמודד עם אתגר ה-IP & design-reuse, ה-Vivado כולל מאגר IPs המבוסס על תקן IP-XACT וכמו כן את כלי ה-IP Packager המאפשר שיתוף IPs בין קבוצות שונות בעזרת יצירת קבצי מעטפת XML ע”פ תקן ה-IP-XACT.

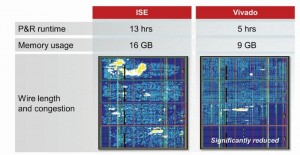

דוגמא ליכולות ה-P&R של ה-Vivado ניתן לראות באיור-2 בהשוואה ל-ISE מהדור הקודם: זמן הריצה קוצר משמעותית מ-13 שעות ל-5 וגם תוצאות ניצול השטח משמעותית טובות יותר.

מזה כשנה עוברת Vivado Design Suite בדיקות ביתא אצל יותר ממאה ועשרים לקוחות ושותפות טכנולוגיות כולל חברות IP וייצרני EDA ולקוחות המשתמשים בהתקני Virtex-7.

“השילוב של ה-Vivado Design Suite עם ה-Virtex®-7 2000T FPGA יצר שינוי פרדיגמה בתעשיית הלוגיקה המתכנתת. ה-Vivado אפשרה לברודקום לתכנן עם ה-FPGA בעל הנפח הגדול ביותר בתעשייה ללא כל צורך בתכנון רצפה ידני או בחציצה”, אומר פול רולף, מנהל הנדסת פיתוח חומרה בברודקום אירופה. “התרשמנו מאוד מהחדשנות Xilinx מספקת, הן בתחום הסיליקון והן בתחום התוכנה”.