.Jonathan Harris, Analog Devices

.Jonathan Harris, Analog Devices

נכון להיום, ממירים אנלוגיים לדיגיטליים (analog to digital converters-ADCs) עוברים מממשקים דיגיטליים מקבילים LVDS ו-CMOS לממשק טורי המכונה JESD204 אשר פותח על-ידי JEDEC

בשעה שהרזולוציה והמהירות של הממירים עלו, כך גדל הביקוש של ממשק יעיל יותר. ממשק ה-JESD204 מספק יעילות זו ומציע מספר יתרונות לעומת הקודמים לו במונחים של מהירות, ממדים ועלות. תכנונים המשתמשים ב-JESD204 נהנים מהיתרונות של ממשק מהיר יותר התואם את הקצב המהיר יותר של קצבי הדגימה של הממירים. בנוסף, קיים צמצום של מספר הפינים הגורם לממדי מארז קטנים יותר ומספר נמוך יותר של נתיבי עקבות (trace routes) המקלים בהרבה על תכנוני הכרטיסים ומציעים עלויות נמוכות יותר בתכנוני הזיווד והכרטיס. התקן גם ניתן להרחבה בנקל כך שניתן לתאמו לקראת צרכים עתידיים. דבר זה הוצג כבר באמצעות שני העדכונים שהתקן כבר עבר. תקן ה-JESD204 עבר כאמור שני עדכונים מאז השקתו ב-2006 ונמצא כעת בעדכון B. בשעה שהתקן אומץ על-ידי יצרנים ולקוחות של ממירים, הוא עבר עידון ונוספו תכונות חדשות אשר העלו את היעילות וקלות המימוש. התקן תואם ממירים אנלוגיים לדיגיטליים (ADCs) כמו גם דיגיטליים לאנלוגיים (DACs), אולם מאמר זה מתמקד ביישום שלו ל-ADCs.

JESD204 (2006)

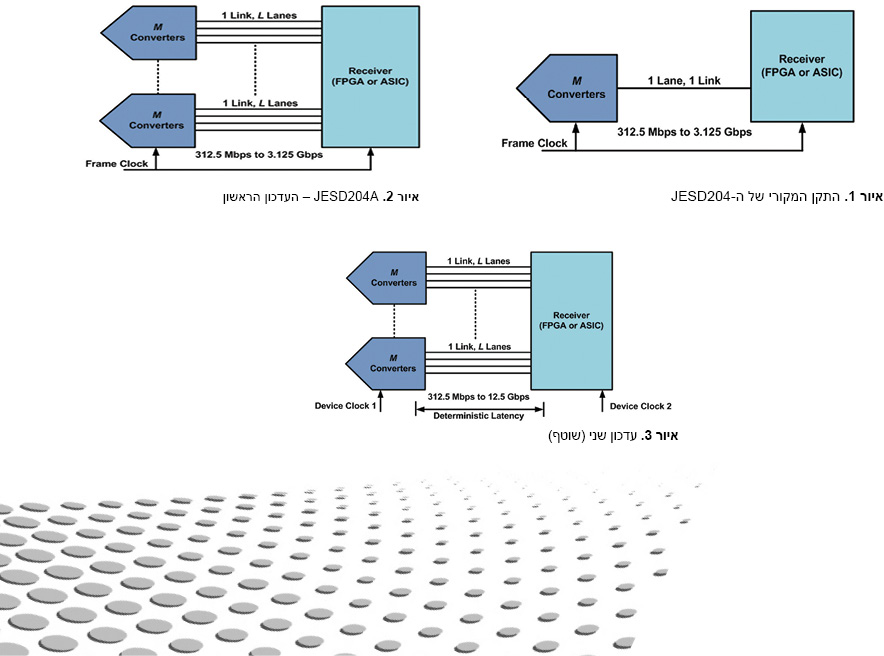

בחודש אפריל 2006 הושקה הגרסה המקורית של ה-JESD204. התקן מתאר קישור של נתונים טוריים רב-גיגה-ביטי בין ממיר(ים) ומקלט, לרוב התקן דוגמת FPGA או ASIC. בגרסה זו, קישור הנתונים הטורי הוגדר עבור נתיב טורי יחיד בין הממיר או ממירים רבים ובין מקלט. תצוגה גראפית מוגשת באיור 1. הנתיב המוצג הוא הממשק הפיזיקאלי בין מספר ממירים

M והמקלט המורכב מזוג הפרשי

של חיבורים הדדיים המשתמש בלוגיקה current mode logic (). הקישור המוצג הוא קישור הנתונים הטורי אשר נקבע בין בממיר(ים) והמקלט. שעון המסגרת מנותב הן לממיר(ים) והן למקלט ומספק את השעון עבור קישור ה-JESD204 בין ההתקנים.

קצב הנתונים של הנתיב מוגדר בין 312.5 מגה-ביט בשנייה (Mbps) ו-3.125 גיגה-ביט בשנייה (Gbps) עם הן עכבת המקור והן של העומס מוגדרות כ-. רמת המתח ההפרשי מוגדרת כ-800 מילי-וולט שיא-לשיא עם תחום רמת מתח במוד המשותף מ-0.72 וולט עד 1.23 וולט. הקישור משתמש בקידוד 8b/10b הכולל שעון מובנה, ומבטל בכך את הצורך בניתוב קו שעון נוסף ואת המורכבות הכרוכה של כוונון אות שעון נוסף, עם הנתונים המשודרים בקצבי נתונים גבוהים.

צורת שידור הנתונים הטוריים מאפשרת שהאפיצות עקבה לעקבה תהיה רוויה ביחס לתכנוני ממשק הדגימה הסינכרוני המקבילי LVDS ו-CMOS. בנוסף, הקידוד הוא מאוזן ב-DC, דבר המבטיח תדר מעבר משמעותי לשימוש עם תכנוני השחזור של השעון והנתונים. הקידוד גם מאפשר שימוש בתווי נתונים ובקרה המגדירים את הכוונון, התחזוקה והניטור של הקישור. התקן מפרט תבניות אימון עם תווי בקרה אלה המאפשרות את כוונון הנתיב בין הממיר(ים) והמקלט דרך הקישור. איכות הקישור מנוטרת במקלט והקישור נקבע וננטש על-ידי המקלט על-פי ספי שגיאה מסוימים המוגדרים על-ידי תקן ה-JESD204. הוכח שהתקן חייב לעבור עדכון כדי לכלול תמיכה עבור נתיבים טוריים מרובים מכוונים עם ממירים מרובים כדי להתאים למהירויות והרזולוציות הגוברות של הממירים.

JESD204A (2008)

בחודש אפריל 2008 הושק העדכון הראשון של התקן, ה-JEDS204A. עדכון זה של התקן הוסיף את היכולת לתמוך בנתיבים טוריים מכוונים מרובים עם ממירים מרובים. קצבי הנתונים של הנתיב הנתמכים נשארו ללא שינוי מהגרסה המקורית של התקן, תוך תמיכה מ-312.5Mbps ועד 3.125Gbps, ושעון המסגרת נשאר על כנו. העלאת היכולות של התקן לתמוך בנתיבים טוריים מכוונים מרובים אפשרה לממירים בעלי קצבי דגימה גבוהים ורזולוציות גבוהות למלא אחר קצב הנתונים הנתמך המרבי של 3.125Gbps. איור 2 מראה תצוגה גראפית של היכולות הנוספות של העדכון כדי לתמוך בנתיבים מרובים.

על-ידי הוספת יכולות אלו לתקן, ניתן היה לתמוך בממירים בעלי קצב דגימה גבוה יותר או רזולוציות גבוהות יותר. לדוגמה, ADC בעל -14ביט הפועל עם שעון דגימות של 250 מגה-הרץ ידרוש קצב נתונים במוצא של

5.0Gbps כאשר הוא משדר מעל קישור אחד עם נתיב אחד כמתואר ב-JESD204. אולם עם העדכון של JESD204A, אפשר היה לתמוך בנתיבים טוריים מכוונים מרובים על הנתיבים הטוריים ואפשר היה למפות את דגימות הממיר בשני נתיבים טוריים מכוונים. דבר זה היה מוריד את קצב הנתונים ל-2.5Gbps לנתיב, הנמצא מתחת לקצב הנתונים הנתמך המרבי של 3.125Gbps. אם כי שתי הגרסאות של התקן, ה-JESD204 המקורי וה-JESD204A המעודכן מציגות ביצועים העולים על ביצועי הממשקים הקודמים, היה עדיין חסר להם גורם עיקרי אחד. גורם חסר זה היה הכמיסות הדטרמיניסטית בנתונים הטוריים בקישור. כאשר דנים ב-ADC, חשוב לדעת את קשר התזמון בין האות הנדגם וההצגה הדיגיטלית שלו כדי לשחזר בצורה נאותה את האות הנדגם במישור האנלוגי לאחר קליטת האות. קשר התזמון הזה מושפע מכמיסות ה-ADC המוגדרת כמספר מחזורי השעון בין רגע הגעת הקצה הדוגם של אות המבוא ועד לזמן כאשר התצוגה הדיגיטלית שלו מופיעה במוצאי ה-ADC. בתקני ה-JEDS204 ו-JEDS204A לא היו יכולות מוגדרות אשר יקבעו בצורה דטרמיניסטית את כמיסות ה-ADC והמוצאים הדיגיטליים הטוריים שלו. בנוסף, הממירים הוסיפו לעלות הן במהירות והן ברזולוציה. גורמים אלה הובילו להולדת העדכון השני של התקן, ה-JEDS204B

JEDS204B

בחודש יולי 2011, הושק העדכון השני של התקן, ה-JEDS204B. אחד המרכיבים העיקריים של התקן המעודכן היה התוספת של המלצות לקביעת הכמיסות הדטרמיניסטית. בנוסף, קצבי הנתונים הנתמכים הועלו עד

12.5Gbps עם דרגות מהירות שונות של ההתקנים המתוארים. עדכון התקן כלל מעבר מהשימוש בשעון מסגרת בתור מקור השעון הראשי לשימוש בשעון ההתקן בתור מקור השעון העיקרי. איור 3 מציג את היכולות הנוספות של העדכון JESD204B.

בשתי הגרסאות הקודמות של תקן ה-JESD204, לא הוגדרו המלצות המבטיחות את הכמיסות הדטרמיניסטית למשך הממשק. העדכון JESD204B מתקן ליקוי זה על-ידי יצירה של מנגנון המבטיח שהכמיסות תהיה הדירה ודטרמיניסטית ממחזור הדלקה אחד לשני ובמהלך סנכרון אירועי הקישור. דבר זה מושג על-ידי יזום רצף כיוונן הנתיב בממיר(ים) בו זמנית לאורך כל הנתיבים ברגע מוגדר היטב בזמן בעזרת שימוש באות מבוא המכונה SYNC~. בנוסף, כל נתיב הנתונים של המקלט צריך להיות חצוץ כדי לפצות על ההיסט לאורך נתיבי הנתונים הטוריים. יש לשחרר חוצצים אלה בו-זמנית ברגע מוגדר היטב בזמן על-ידי שימוש במספר מחזורים המכונים Rx Buffer Delay () הניתנים לתכנות.

בנוסף לכמיסות הדטרמיניסטית, גרסת ה-JESD204B מעלה את קצבי נתוני הנתיב הנתמכים עד 12.5Gbps ומחלקת את ההתקנים לשלוש דרגות מהירות. דרגת המהירות הראשונה מתכווננת עם קצבי נתוני הנתיב מהגרסאות JESD204 ו-JESD204A של התקן ומגדירה את הממשק החשמלי עבור קצבי נתוני הנתיב עד 3.125Gbps. כפי שצוין מקודם, רמת המתח ההפרשי בקצבי נתונים אלה היא 800 מילי-וולט שיא-לשיא עם תחום רמת מתח במוד משותף מ-0.72 וולט עד 1.23 וולט כאשר שתי עכבות המקור והעומס מוגדרות כ-.

דרגת המהירות השנייה ב-JESD204B מגדירה את הממשק החשמלי עבור קצבי נתונים בנתיב עד 6.375Gbps. דרגת מהירות זו דומה לדרגת המהירות הראשונה בכך שרמת המתח ההפרשי היא 800 מילי-וולט שיא-לשיא נומינלי. לתחום רמת המתח במוד משותף יש כמה הבדלים קטנים המבוססים על מתח הסיומת המוגדר במקלט, אך הוא ככלל דומה לדרגת המהירות הראשונה. עכבת המקור והעומס היא זהה ומוגדרת כ-.

דרגת המהירות השלישית ב-JESD204B מגדירה את הממשק החשמלי עבור קצבי נתונים בנתיב עד 12.5Gbps. דרגת מהירות זו מנמיכה את רמת המתח ההפרשי הדרוש עבור הממשק החשמלי ל-400 מילי-וולט שיא-לשיא, דבר המפחית את הרמות הדרושות בגורם של 2 בהשוואה לשתי דרגות המהירות הנמוכות יותר. תחום רמת המתח במוד משותף דומה לדרגת המהירות השנייה ותלוי במתח הסיומת המוגדר במקלט. שוב, שתי העכבות של המקור והעומס מוגדרות כ-.

כדי לאפשר גמישות יתר, עדכון ה-JESD204B עובר משעון מסגרת לשעון התקן. לפני כן, בעדכונים JESD204 ו-JESD204A, שעון המסגרת שימש כייחוס התזמון המוחלט במערכת JESD204. שעון המסגרת ושעון הדגימה של הממיר(ים) היה בד"כ זהה. דבר זה לא אפשר גמישות מרובה ויכול היה לגרום למורכבות בלתי-רצויה בתכנון המערכת כאשר היה ניסיון לנתב את האות להתקנים מרובים ולפצות עבור כל סטייה בין מסלולי הניתוב השונים. ב-JESD204B, שעון ההתקן משמש כייחוס תזמון עבור כל מרכיב במערכת JESD204. כל ממיר ומקלט מקבל את שעון ההתקן המתאים שלו ממעגל מחולל השעון האחראי להפקת כל שעוני ההתקנים ממקור משותף. דבר זה מאפשר גמישות יתר בתכנון המערכת, אך דורש שהקשר בין שעון המסגרת ושעון ההתקן יהיה מוגדר עבור התקן נתון. עם עליית המהירות והרזולוציה של הממירים, גברה הדרישה לממשק דיגיטלי יותר יעיל. ממשק הנתונים הטוריים של JESD204 נוצר כדי להציע דרך יותר טובה ויותר מהירה להעביר נתונים מהממירים אל התקני המקלט. הממשק עבר שני עדכונים כדי לשפר את מימושו ולמלא אחר הדרישות הגוברות שנוצרו בעקבות המהירויות הגבוהות יותר והרזולוציות הגבוהות יותר של הממירים. כל עדכון ענה לדרישות לשיפורים במימוש שלו ואפשר לתקן להתפתח כדי למלא את הדרישות החדשות שנוצרו בעקבות השינויים בטכנולוגיה של הממירים. בשעה שתכנוני המערכת הפכו ליותר מורכבים וביצועי הממיר עלו, תקן ה-JESD204 אמור להתאים ולהתפתח כדי להמשיך ולמלא אחר דרישות התכנון החדשות המחייבות.

סימוכין

JEDEC Standard JESD204 (April 2006). JEDEC Solid State Technology Association. www.jedec.org

JEDEC Standard JESD204A (April 2008). JEDEC Solid State Technology Association. www.jedec.org

JEDEC Standard JESD204B (July 2011). JEDEC Solid State Technology Association. www.jedec.org