תכנון וניפוי של מעגל עניבה נעולת-מופע ( – phase-locked loop) עשויים להיות מורכבים, אלא אם כן למהנדסים יש הבנה מעמיקה של תורת ה-PLL והם בעלי תהליך פיתוח לוגי. מאמר זה מציג שיטה מפושטת של תכנון PLL ומספק דרך יעילה והגיונית לניפוי בעיות PLL קשות.

הדמיה

קשה להעריך את מפרטי מעגל PLL מבלי לדמות אותו בתנאים מיוחדים, כך שהדמיה צריכה להיות הצעד הראשון בתהליך תכנון של PLL. אנחנו ממליצים שהמהנדסים ישתמשו בתוכנת ADIsimPLL כדי להריץ הדמיה המבוססת על דרישות המערכת שלהם, כולל מגבלות של תדר ייחוס, תדר צעד, רעש מופע (ריצוד) ותמריץ תדר.

מהנדסים רבים מבולבלים כיצד לבחור תדר ייחוס, אך הקשר בין צעד תדר הייחוס ותדר המוצא הוא פשוט. ב-PLL של integer-N, הצעד של תדר המוצא שווה לתדר במבוא של גלאי המופע-תדר (phase-frequency detector – PFD), שהוא תדר הייחוס מחולק במחלק הייחוס, R. ב-PLL של fractional-N, הצעד של תדר המוצא שווה לתדר המבוא PFD מחולק לערך ה-MOD, כך שניתן להשתמש בתדר ייחוס גבוה יותר כדי לקבל צעד תדר קטן יותר. בשעה שמחליטים האם להשתמש ב-integer-N או fractional-N, ניתן להחליף את צעד התדר ברעש מופע, כאשר תדר PFD נמוך יותר מספק רזולוציית תדר מוצא טובה יותר, אך רעש מופע גרוע יותר.

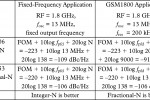

כדוגמה, טבלה 1 מראה שאם הדרישה מחייבת מוצא תדר קבוע עם צעד תדר גדול מאוד, PLL integer-N, דוגמת ה-ADF4106 הוא עדיף בשל רעש המופע הכולל בתוך התחום (in-band) טוב יותר. לחילופין, אם הדרישה היא עבור צעד תדר קטן, PLL fractional-N, דוגמת ה-ADF4153 הוא עדיף מאחר שהרעש הכולל שלו הוא טוב יותר מאשר זה של ה-PLL integer-N. רעש מופע הוא נתון PLL מהותי, אולם דף הנתונים איננו יכול לנקוב בביצועים עבור כל היישומים האפשריים. לכן, הדמיה ולאחריה בדיקה של החומרה המעשית היא חיונית.

גם כאשר משתמשים ב-ADIsimPLL כדי לדמות מעגל PLL בתנאים אמיתיים, התוצאות יהיו כנראה בלתי מספיקות אלא אם כלולים תיקי דגם עבור הייחוס המעשי והמתנד מבוקר מתח (voltage-controlled oscillator -). במידה שלא כך, המדמה ישתמש בייחוס ו-VCO אידיאליים כדי לבצע הדמיה. הזמן הדרוש כדי לערוך תיק ספריה עבור מקור ה-VCO וייחוס יהיה מוצדק בהחלט כאשר דרוש דיוק הדמיה גבוה.

PLLs משתמשים במערכת בקרה עם משוב שלילי הדומה לזו של מגבר, כך שהמושגים של רוחב-פס לולאה ומרווח המופע (phase margin) תקפים גם כאן. ככלל, יש לקבוע את רוחב-הפס של הלולאה שיהיה יותר קטן מאשר עשירית תדר ה-PFD, והתחום הבטוח עבור מרווח המופע הוא מ-450 ל-600. בנוסף, יש לבצע הן את ההדמיה והן את יצירת האב-טיפוס בכרטיס ממשי כדי לאשר שהמעגל יענה למפרט בהתחשב במרכיבים הפרזיטיים על מערך המעגל המודפס והאפיצויות של הנגדים והקבלים במסנן הלולאה.

לעתים לא ניתן להשיג ערכים מתאימים של נגדים וקבלים, כך שעל המהנדסים לקבוע האם ערכים אחרים אכן יהיו תקפים. פונקציה קטנה המכונה BUILT מוחבאת בתפריט ה-Tools של ה-ADIsimPLL. פונקציה זו משנה את ערכי הנגדים והקבלים אל הערך ההנדסי התקני הקרוב ביותר, ומאפשרת למתכנן להריץ מחדש את ההדמיה כדי לבדוק את הערכים החדשים עבור מרווח המופע ורוחב הפס של הלולאה.

אוגרים (registers)

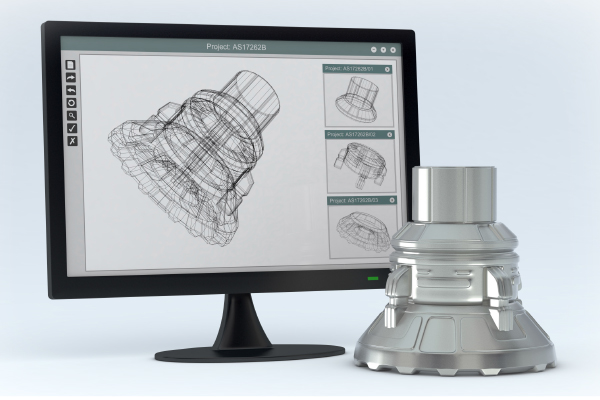

PLLs של ADI מספקים אופציות רבות הניתנות לעיצוב על-ידי המשתמש כדי לאפשר סביבת תכנון גמישה, אך הדבר יוצר את האתגר של קביעת הערכים שיש לאכסן בכל אוגר. פיתרון נוח הוא להשתמש בתוכנת ההערכה כדי לקבוע את ערכי האוגר, אף אם המעגל המודפס איננו מחובר למדמה. לאחר מכן, ניתן לקבוע את תיק ההערכה כ-stp. file או להוריד אותו אל כרטיס ההערכה. תוצאות ההדמיה של ADIsimPLL, המוצגות באיור 1, ממליצות על ערכי האוגר עבור פרמטרים כגון זרם הליבה של ה-VCO.

סכימות ותסדיר המעגל

יש לזכור מספר דברים כאשר מתכננים מעגל PLL שלם. ראשית, חשוב להתאים את העכבה במבוא הייחוס של ה-PLL כדי למזער החזרות. כמו כן, שמור על קיבול קטן במקביל לפיתחת המבוא, כי הוא יפחית את קצב הסבב של האות המגיע ויוסיף רעש ללולאת ה-PLL. עיין בדרישות המבוא בדף הנתונים של ה-PLL כדי לקבל מידע מפורט יותר.

שנית, הפרד בין ספקי הכוח האנלוגי והדיגיטלי כדי למזער את ההפרעה ביניהם. ספק ה-VCO הוא במיוחד רגיש, כך שדורבנים ורעש כאן יכולים בנקל להתחבר למוצא. נא להתייחס ל-Powering a Fractional-N Voltage Controlled

Oscillator (VCO) with Low Noise LDO Regulators for Reduced Phase Noise

() לקבלת אזהרות נוספות ומידע מפורט יותר.

שלישית, יש למקם את הנגדים והקבלים המשמשים למימוש מסנן הלולאה קרוב ככל האפשר לשבב ה-PLL תוך שימוש בערכים אשר הומלצו בתיק ההדמיה. אם אתה מתקשה בנעילה על אות לאחר ששינית את ערכי מרכיבי מסנן הלולאה, אנא נסה את הערכים המקוריים אשר שימשו בכרטיס ההערכה.

באשר לתסדיר המעגל, העיקרון הראשי הוא להפריד את המבוא מהמוצא, ולוודא שהמעגלים הדיגיטליים אינם מפריעים למעגלים האנלוגיים. לדוגמה, מיקום פס ה-SPI קרוב מידי למבוא הייחוס או למוצא ה-VCO יגרום לדורבנים במוצא ה-PLL כאשר ניגשים לאוגרי ה-PLL.

מבחינת התכנון התרמי, הנח רפידת הארקה תרמית מתחת לשבב ה-PLL כדי להבטיח שהחום זורם דרך הרפידה אל המעגל המודפס וגוף הקירור. על המתכננים לחשב את כל הפרמטרים של שבב ה-PLL והמעגל כאשר הם משמשים בתנאים קיצוניים.

שימוש יעיל ב-MUXOUT

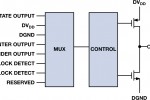

בתחילת שלב הניפוי, קשה לקבוע היכן להתחיל כאשר ה-PLL אינו ננעל. כצעד ראשון, השתמש ב-MUXOUT כדי לראות אם כל יחידה פונקציונלית פנימית מתפקדת נכון, כמתואר באיור 2. לדוגמה, MUXOUT יכול להציג את המוצא של ה-R-counter כדי להראות שאות מבוא הייחוס הוא תקין והתוכן של האוגר נכתב בהצלחה. MUXOUT יכול גם לבדוק את מצב הנעילה של הגלאי והמוצא של מחלק ה-N בלולאת המשוב. בדרך זו, המתכנן יכול לאשר האם הערך של כל מחלק, שבח או תדר הוא נכון. זהו התהליך הבסיסי של ניפוי PLL.

ניתוח במישור הזמן

כאשר אתה מנפה PLL, השתמש בניתוח במישור הזמן כדי להוכיח שהנתונים הכתובים אל האוגרים בפס הממשק הטורי ההיקפי (serial peripheral interface-SPI) הם נכונים. גם אם הקריאה והכתיבה לא נערכו מהר ביותר, הבטח שתזמון ה-SPI מתאים למפרטים ושערב-הדיבור (crosstalk) בין הקווים השונים ממוזער.

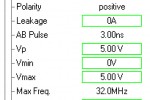

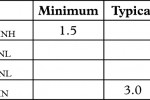

יש לעיין בדיאגרמת התזמון של דף הנתונים של ה-PLL כדי לקבוע את זמן עריכת הנתונים, מהירות השעון, רוחב הפולס ומפרטים אחרים. וודא שהשארת מספיק מרווח כדי להבטיח שדרישות התזמון נענות בכל התנאים. יש להשתמש באוסילוסקופ כדי לוודא שהשעון וקצות הנתונים נמצאים במצב הנכון במישור הזמן. אם קווי השעון והנתונים קרובים מידי, ערב-דיבור יגרום שאנרגיה מהשעון תתחבר לקו הנתונים דרך עקבות המעגל. חיבור זה יגרום לתקלה בקו הנתונים המופיעה על הקצה העולה של השעון. לכן, הבט על שני קווים אלה כאשר אתה כותב או קורא את האוגרים, במיוחד אם מופיעות שגיאות באוגר. הבטח שהמתח על הקווים מסופק כמתואר בטבלה 2.

ניתוח ספקטראלי

סוגיות במישור התדר הן שכיחות ומורכבות יותר. בעזרת נתח ספקטרום, בדוק ראשית כל אם מוצא ה-PLL נעול, כמתואר על-ידי שיא תדר יציב. אם לאו, יש לבצע את הרמזים שתוארו לעיל.

אם ה-PLL נעול, צמצם את רוחב-הפס של נתח הספקטרום כדי לקבוע באם רעש המופע הוא סביר או לא, והשווה את תוצאת הבדיקה עם תוצאת ההדמיה. מדוד את רעש המופע ברוחבי-פס אחדים, כגון 1 קילו-הרץ, 10 קילו-הרץ ו-1 מגה-הרץ, לדוגמה.

אם התוצאה איננה כמצופה, בחון ראשית את תכנון מסנן הלולאה ובדוק את הערכים הממשיים של הרכיבים על הכרטיס. שנית, בדוק את מבוא הייחוס כדי לראות אם רעש המופע שלו הוא שווה להדמיה. רעש המופע המדומה של ה-PLL צריך להיות דומה לתוצאה הממשית אלא אם התנאים החיצוניים שונים או שהאוגרים נכתבו בערכים מוטעים.

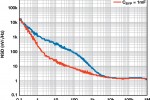

אין להתעלם מהרעש מספק הכוח, אף אם משתמשים ב-LDO נמוך-רעש, מאחר שממירי ה-dc-to-dc וה-LDOs נראים כמו מקורות רעש. דף הנתונים של ה-LDO מראה בד"כ צפיפות ספקטרום הרעש אשר תשפיע על חלקים רגישים לרעש דוגמת PLLs (ראה איור 3). בחר מקור הספק נמוך-רעש עבור ה-PLL, במיוחד כדי לספק את זרם הליבה של ה-VCO.

ארבעה סוגי דורבנים מופיעים לרוב במוצא ה-PLL:PFD או דורבני ייחוס, דורבנים של שברים, דורבנים של גבולות המספר השלם ודורבנים ממקורות חיצוניים, כמו ספק הכוח. לכל ה-PLLs יש לפחות סוג אחד של דורבן, ואם כי לא ניתן להרחיק אותם כליל, אנחנו יכולים לעתים לשפר את הביצועים הכלליים על-ידי המרה של סוג אחד של דורבן באחר.

כדי למנוע דורבני ייחוס, בדוק את הקצה העולה של אות הייחוס. קצה שהוא מידי מהיר או מידי גדול באמפליטודה יגרום להרמוניות חזקות במישור התדר. כמו כן, בדוק בזהירות את תסדיר הכרטיס כדי למנוע ערב-דיבור בין המבוא והמוצא.

כדי למזער דורבנים של שברים, ניתן להוסיף רעד כדי להעביר את הדורבנים של שברים אל ריצפת הרעש, אך הדבר יעלה במעט את רצפת הרעש.

דורבנים של גבולות המספר השלם הם נדירים, ומופיעים רק אם תדר המוצא קרוב מידי למכפלה שלימה של תדר הייחוס כך שמסנן הלולאה לא יכול למנוע זאת. דרך קלה לפתור בעיה זו היא לשנות את תכנית תדר הייחוס. לדוגמה, אם דורבן ייחוס מופיע ב-1100 מגה-הרץ עם מוצא של 1100.1 מגה-הרץ, מבוא ייחוס של 20 מגה-הרץ ו-מסנן לולאה של 100 קילו-הרץ, שינוי תדר הייחוס ל-30 מגה-הרץ יבטל את הדורבן.

סיכום

התהליך של ניפוי PLL דורש הבנה מעמיקה של ה-PLL, וניתן למנוע הרבה בעיות על-ידי מתן תשומת-לב קרובה במהלך שלב התכנון. אם נוצרות סוגיות במשך שלב הניפוי, נא מלא אחר ההצעות הכלולות במאמר זה כדי לנתח את הסוגיות אחת לאחת ולתקוף אותן בהדרגה. לשם מידע נוסף, נא התייחס לשלל המידע הרלוונטי שניתן למצוא באתר החברה.

סימוכין

Curtin, Mike, and Paul O’Brien.“Phase-Locked Loops for High-Frequency Receivers and Transmitters-Part 1.” Analog Dialogue, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O’Brien. “Phase-Locked Loops for

High-Frequency Receivers and Transmitters-Part 2.” Analog

Dialogue, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O’Brien, “Phase-Locked Loops for

High-Frequency Receivers and Transmitters-Part 3.” Analog

Dialogue, Volume 33, Number 1, 1999.

CN0147 Circuit Note. Powering a Fractional-N Voltage

Controlled Oscillator (VCO) with Low Noise LDO Regulators

for Reduced Phase Noise.

Fox, Adrian. “PLL Synthesizers (Ask the Applications

Engineer-30).” Analog Dialogue, Volume 36, Number 3, 2002.

MT-086 Tutorial. Fundamentals of Phase-Locked Loops (PLLs)

המחבר

Ray Sun קיבל תואר BEng מ-Wuhan University of Technology ב-2002, הצטרף ל-Analog Devices ב-2009 וקיבל תואר MBA מ-Huazhong University of Science & Technology ב-2010. בתור מהנדס יישומי שדה הממוקם ב-Wuhan, סין, Ray תומך עתה בלקוחות במרכז סין. בזמנו הפנוי, Ray פועל כמאלף כלבים, מתנגד לניסויים בחיות ומשמש כחבר charter של Toastmasters ב-Wuhan.

- טבלה 1. רעש המופע קובע את בחירת ה-PLL

- איור 1. תוכנת ההדמיה של ADIsimPLL מספקת ערכים מומלצים עבור אוגרי העריכה

- איור 2. פין ה-MUXOUT מסייע לתהליך הניפוי של ה-PLL

- טבלה 2. מבואות לוגיים

- איור 3. צפיפות ספקטראלית של רעש LDO