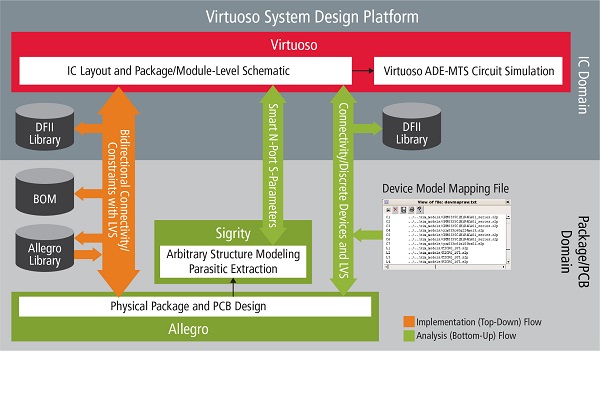

קיידנס דיזיין סיסטמס (Cadence) הכריזה על ה- Cadence® Virtuoso® System Design Platform- זרימת אימות ותכנון משותפים אוטומטית, יעילה ורשמית בין פלטפורמת ה-Cadence Virtuoso לבין טכנולוגיות Allegro ו-Sigrity. רמת אינטגרציה גבוהה זו מאפשרת למהנדסים לבצע תכנון בו זמני בשבב, מארז ולוח. הפלטפורמה החדשה הופכת תהליכים שהיו עד כה ידניים לאוטומטיים ולפיכך מצמצמת שגיאות ומסוגלת להפחית את זמן ה-LVS (layout versus schematic) בין ה-IC ל-Package.

עד כה ההתפתחויות בטכנולוגיות הסיליקון היו טובות דיין עבור השיפורים השוטפים במוצרי מיקרו-אלקטרוניקה, אך לנוכח המורכבות ההולכת וגדלה של השבבים, החבילות והלוחות הקיימים היום גובר הצורך במעגלים משולבים המתבססים הן על חומרי סיליקון והן על חומרים שאינם סיליקון לצורך תכנון מטבי של מערכות עתירות ביצועים. כתוצאה מכך, המגמה הזו מניעה את הצורך של מהנדסים לשלב ריבוי של טכנולוגיות הטרוגניות בתוך מוצר אחד יחיד, מה שמשפיע על הביצועים ועל הפונקציונליות של המעגלים המשולבים ויוצר מערך חדש של אתגרים עבור חברות המוליכים למחצה. כדי להתמודד עם האתגרים הללו פיתחה קיידנס פתרון חדשני וחוצה-פלטפורמות שמוסיף יעילות ואוטומציה לתכנון של מארזים או מודולים הכוללים התקני off-chip וריבוי מעגלים משולבים המבוססים על PDKs (ערכות תכנון תהליך) שונות.

ה-Virtuoso System Platform מאפשרת למתכנני המעגלים המשולבים לכלול בקלות איתור רכיבים פרזיטיים של המערך ברמת המערכת בתוך מתודולוגיית אימות ה-IC, מה שמאפשר חיסכון בזמן תודות לשילוב של נתוני חיבוריות מערך מארז/לוח עם המודל החשמלי הפרזיטי במערך ה-IC. לאחר מכן נוצרת באופן אוטומטי סכמה "מודעת למערכת" שיכולה לשמש בקלות ליצירת מערך בדיקות עבור הסימולציה הסופית ברמת המעגל. הפלטפורמה החדשה מביאה אוטומציה אל כל המתודולוגיה, מה שמבטל את הצורך בתהליך הידני והמועד לטעויות של שילוב מודלים של פרזיטים ברמת המערכת בחזרה אל הזרימה של מתכנן המעגל.