בימינו, החברה נמצאת במצב של תקשורת מתמדת. באמצעות יישומים כמו Facebook ,Twitter ו Instagram, על טרהבייטים של דאטה להיות מועברים במהירויות שגדלות כל הזמן.

מהנדסי אלקטרוניקה ניצבים בחזית האתגר הזה, להגדיל מהירות העברת דאטה במערכות שגודלן הפיזי הולך וקטן כל הזמן ומורכבותן גדלה כל הזמן.

עבור חברה כמו Facebook למשל, מהירות ורוחב פס בתקשורת שרתים הם פרמטרים קריטיים. על תשתיות התקשורת להיות מסוגלות לסנן ולמיין נתונים בתוך טרהבייטים של דאטה תוך שברירי שניה. אפילו משימה פשוטה לכאורה כמו זיהוי אנשים שנהנים ממסעדה מסוימת למשל דורשת תכונות תקשורת שרתים יוצאות דופן.

בכל תשתיות התקשורת, הרכיבים הקריטיים ביותר הם מתגי ה ASIC ברשת ומודולים אופטיים. שבבים גדולים ועתירי כוח נושאים בנטל העברת המסה של כל הטרהבייטים האלה אל במודולים האלקטרו אופטיים אשר ממירים את האותות האלקטרוניים לאור. אותו אור עושה את דרכו ליעד מוגדר באמצעות רשתות של סיבים אופטיים.

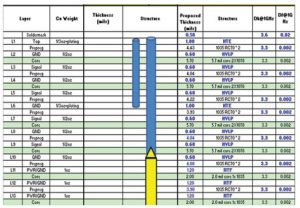

טבלה מס’ 1

בתהליך התכנון והפיתוח של רכיבי רשת מהירים קריטיים, על מהנדסים לתת תוקף למאפיינים של הרכיבים. באופן טיפוסי, תהליך זה מתחיל עם תכנון של אב טיפוס של מעגל מודפס שעליו יהיה מותקן הרכיב לצורך מדידה ובדיקה. בבדיקות אפיון מוקדמות האותות המהירים בד”כ מוזנים קרוב ככל האפשר לרכיב הנמדד, כדי לאפשר למהנדסים למדוד את ביצועי הרכיב הנמדד באופן נקי ככל שניתן.

מהנדסים יבחרו חומרים שמסוגלים לעבוד במהירויות גבוהות במיוחד על מנת לצמצם למינימום את האיבוד בקו התמסורת. המהנדס חייב גם ליצור מעבר בעל עכבה מבוקרת למחבר בקצה קו התמסורת. אותו מחבר ישמש לצורך החיבור לציוד הבדיקה (PNA / bert / TDR וכו’).

תוך שימת דגש רב על המעגל המודפס והחיבורים, לעיתים קרובות נוטים מהנדסים להזניח את הסימולציה ותכנון מוקפד של המעברים בין רכיב לרכיב על המעגל המודפס.

בהמשך המאמר הזה נחקור וננתח את מערך השכבות של מעגל מודפס טיפוסי שתוכנן עבור אפיון אלקטרוני של רכיב ל PCI-E Gen 3 ונשווה בין מס’ שיקולי ייצור שמשפיעים על ביצועי קו התמסורת בכללותו.

בטבלה הבאה (טבלה מס’ 1) מערך שכבות של מעגל מודפס בו נעשה שימוש לצורך הסימולציה המתוארת במאמר זה. 6 השכבות העליונות הן בעצם חלק מן ה sub-lamination והן מוצבות מעל מערך השכבות של המעגל המודפס. באופן זה ל 6 השכבות העליונות יש תהליך ייצור נפרד שחייבים להתחשב בו כאשר מנסים למצוא תכנון וביצועים מיטביים במעגל המודפס.

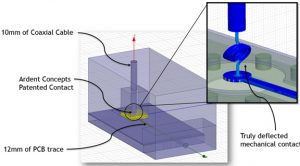

תמונה מס’ 1

החיבור אותו אנו מציגים הוא Multicoax assembly ללא בדיל שפותח ומיוצר ע”י חברת Ardent Concepts אשר נציגתה בישראל היא MTI Summit Electronics.

דוגמא ל simulation setup מוצגת בתמונה מס’ 1. התמונה מציגה את המעגל בתצורת microstrip אך תוצאות הסימולציה למטה הן בתצורת internal strip-line:

לצורך הסימולציות התמקדנו בכיוונים של המעבר מן המחבר אל קו ה 50 אוהם במעגל המודפס. זה כולל את ה anti-pads, capture-pads, via diameters, via stubs וכו’. אולם, מכיוון שאין שליטה על כניסת קואקס ואורך הקו כולל, איננו מחשיבים את האורך הכולל של ה transmission line בסימולציה ובמקום זה כללנו קואקס קצר וקו תמסורת מודפס כך שלאות יש מספיק זמן להתייצב בכל חלק בלתי תלוי.

Strip-line routing on layer 3, with no via stub

טכנולוגיה זו של קידוח via ידועה כ blind via. בתרחיש זה ה via מחוברת רק מן ה launching layer אל ה signal layer. ישנן מגבלות בטכנולוגיה זו ובעומק ה blind via. בגלל היחס בין קוטר הקידוח ואורכו (aspect ratio), רוב ה blind vias מוגבלים ל 3 שכבות, מוכר כ 2 deep blind via. Blind vias לעיתים מכונים microvias ומאפשרים קידוחים ו capture pad קטנים במיוחד.

Strip-Line routing on layer 3, with 10 mil via stub

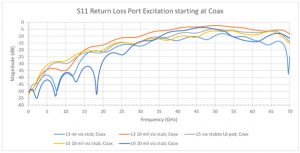

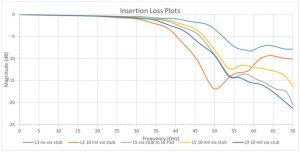

גרף מס’ 1

הגישה המקובלת ביותר עבור מעברי via היא קידוח עובר. בתרחיש זה קודחים חור דרך המעגל ומצפים אותו. הדבר מייצר חיבור בין ה launching layer ל signal layer. אולם, באופן זה נוצר חיבור בין שתי שכבות אלה ויתר השכבות הלא רצויות מתחת. כדי להיפטר מן החיבורים האלה נקדח שוב מן הצד השני, קידוח שיעצור סמוך ל signal layer. כאשר נעשה שימוש בתהליך המתואר נקבל “שארית” של via תחת ה capture pad, והיא בעצם ה via stub. למרבה הצער תוצר לוואי של הטולרנסים הסטנדרטיים של קידוח ה via הם via stubs אשר קשה לצפות את אורכם. אורך ה stub יכול להגיע עד ל 12 mil והוא התורם הגדול ביותר לירידה באיכות האות בסימולציה מסוג זה.

Strip-line routing on Layer 5, with a via to Layer 6, where there is a capture pad on Layer 6

כפי שהוזכר קודם, 6 השכבות העליונות הן sublamination, כלומר מטופלות כמעגל מודפס עצמאי ונפרד. אולם, ישנן מס’ טכניקות ייצור מקובלות. לדוגמא, יש via stub בין שכבה 5 ושכבה 6, במקום שאנו רוצים לנתב את שכבה 5, היכן שקים גם capture pad משעת תהליך חיבור המעגליםהמודפסים יחדיו.

יתר תצורות הניתוב דומות לתיאור של Layer 3 with 10 mil via stub. אולם, שכבות האותות הן שכבה 5 ושכבה 9, בהתאמה. יש לציין שבמעגל המודפס המדובר, בגלל תהליך ה sublamination, בלתי אפשרי לקבל via stub באורך 10 mil בשכבה 5. אולם, הסימולציה בוצעה לצורך ניתוח השוואתי.

לפני קבלת התוצאות ננסה לעשות מספר ניחושים מושכלים לגבי תצורת הניתוב בעלת הביצועים הטובים ביותר. להלן הסדר, מן הטוב ביותר לגרוע ביותר:

ניתוב באמצעות strip-line בשכבה 3 ללא כל via stub

ניתוב באמצעות strip-line בשכבה 3, עם via stub באורך 10 mil

ניתוב באמצעות strip-line בשכבה 5, עם via לשכבה 6, היכן שקיים capture pad בשכבה 6

ניתוב באמצעות strip-line בשכבה 5, עם via stub באורך 10 mil

ניתוב באמצעות strip-line בשכבה 9, עם via stub באורך 10 mil

גרף מס’ 1 מציג את ה s-parameters של S11, return loss. מסע האות מתחיל בכבל הקואקסיאלי ומסתיים ב PCB trace. כפי שניתן לראות בתרשים חלק מן הניחושים שעשינו הוכחו כנכונים.

ניתן לראות שעבור תדרים נמוכים מ

גרף מס’ 2

28 GHz, התצורה של שכבה 9 עם via stub באורך 10 mil עובדת באופן הטוב ביותר. זו עובדה מעניינת מכיוון שזה המעבר הארוך ביותר. אולם, זה גם מראה שבזכות אורך המעבר יש לאות זמן רב יותר להתייצבות ויש יותר אפשרויות לכוון anti-pads סביב ה signal via במטרה לשלוט באמצעות כוונון על העכבה. אבל, מה שנכון לתדרים נמוכים יותר לא עובד טוב בתדרים גבוהים יותר. כאשר אורך הגל קטן, קו התמסורת הארוך גורם להחזרות עד כדי השפעה על הביצועים בתדרים גבוהים יותר. יש לציין כי ה return loss משתפר משמעותית מעל 55 GHz בתצורת הניתוב בשכבה 9, מה שאומר שיש תחום תדרי תהודה באזור ה 35 – 53 GHz.

בממוצע אנו רואים שלתצורה של ניתוב דרך שכבה 3 ללא via stub הביצועים הכלליים הטובים ביותר. בתדרים נמוכים ניתן לראות בגרף מס’ 2 שהביצועים בתצורה זו עולים על ביצועי שאר התצורות. עובדה זו מיוחסת לאורך ה via הכללי הקצר, שהוא בערך 13 mil מלמעלה ועד שכבה 3. כאשר יש מעבר מספיק קצר יכולות להתרחש החזרות מכיוון שאין מספיק זמן לאות להתייצב. הדבר בולט יותר כאשר בוחנים את תצורת שכבה 3 עם via stub באורך 10 mil.

ניתן לחשוב שאורך המעבר הקצר יגרום לתצורת ניתוב של שכבה 3 עם via stub באורך 10mil להיות בעלת ביצועים טובים יותר מן התצורה של שכבות 5 / 9. אולם, כפי שלמדנו קודם, האורך הקצר בצמוד לvia stub ארוך יחסית עשוי לגרום לתוהו ובוהו בביצועים הכלליים.

לסיכום, ניתן לשקול בין שתי התצורות לניתוב בשכבה 5 אך הדרך הטובה באמת בתצורה של המעגל המודפס בו אנו דנים היא via stub לשכבה 6 עם capture pad באורך 20 mil בשכבה 6. אורך ה via stub בתרחיש הזה הוא 5.2 mil. למרות ש ה – via stub קצר מן ה – 10 mil, התוספת של ה capture pad בשכבה 6 יוצר גאומטריה נוספת לקרינה של האות. נכון שלו היה ה via stub קצר יותר וללא ה capture pad היו הביצועים טובים יותר מאשר אלו עם ה 10 mil via stub אולם מה שנוכחנו לדעת הוא שתוספת ה capture pad הניבה ביצועים כמעט זהים.

ניתן לראות כי בד”כ ניחות המעבר די עוקב אחר הנחות המקור בעניין ביצועים טובים / גרועים.

יוצא הדופן העיקרי, שוב, היא שכבה 3 עם via stub באורך 10 mil. לא רק ש ה – via הקצר גורם ליותר החזרות, גם היחס בין ה – via stub ו ה – via עצמה בתצורה זו מאפשרת להרבה יותר אנרגיה לברוח החוצה בתחום התדרים שבין 35 GHz ל – 50 GHz.

מה המסקנות מהדוגמא הקטנה הזו?

אידיאלית, אנו רוצים להקטין את אורכי ה via stubs. Via stubs הם בעצם אנטנות ועשויים גם להוסיף קיבול, מה שפוגע בעכבה. אולם, עלינו גם לקחת בחשבון שמעבר קצר יותר באורכו הכללי לא בהכרח טוב יותר, כמו שנוכחנו בבדיקות של ניתוב אותות בשכבות העליונות. למרות שזה לא תמיד נכון, תלוי בעובי השכבה, ניתוב אותות בשכבות העליונות יכול ליצור מעבר קצר מידי שיגרום להחזרות בלתי רצויות.

תמונה מס’ 2

זהו רק מעבר אחד מיני רבים במעגל המודפס, ושיקולים דומים צריכים להיעשות לגבי כל המעברים המיועדים למעבר אותות במהירויות גבוהות. לדוגמא, חשוב לערוך ניתוח דומה למעבר ה – via לרכיב הנבדק, BGA ASIC לדוגמא, שמולחם ישירות או מותקן על socket מתאים.

בעוד קווים מנחים חדשים לביצועים מפותחים ומפורסמים על בסיס יומי, גם ניתוח זה של מעברים וערוצים מהירים מתפתח כל הזמן. תהליכים שהיו נהוגים אתמול אינם ישימים יותר ונדרשת בחינה מחדש באופן קבוע של תכנון המעגל המודפס, וכן של טכנולוגיות הייצור המעורבות בתהליך. לא מספיק לדעת כיצד לתכנן את הערוץ או המעבר לביצועים מיטביים, עלינו להשיג לעצמנו את היכולות והמשאבים לייצור המעגל המודפס באופן מיטבי. לעיתים קרובות מידי לקוחות מתלוננים שאינם יכולים להדק טולרנסים בגלל מגבלות של יצרני ה PCB. שיקולי תקציב מובנים כמובן אך עלינו להבין שאם אנחנו ממשיכים להשקיע משאבים ואנרגיה בפיתוח מוצרים חדשים, עלינו להיות מוכנים לעשות את הצעד הנוסף קדימה כדי ליצור את הכלים הנחוצים למדידת והערכת המוצרים שלנו.

חברת Ardent Concepts מתמחה בפתרונות של Signal Integrity. סדרת מוצרי ה TR Multicoax (תמונה מס’ 2) שלהם מספקת Signal Integrity מהדרגה הגבוהה ביותר ממספר רב של ערוצים מהירים, דיגיטליים ואנלוגיים. ניתן לבחור בין מס’ תצורות לתדרים שונים, עד 20 GHz, 40 GHz ו 70 GHz, ובקרוב גם 110 GHz, והמשתמשים יכולים לשדרג את המחברים שלהם ככל שדרישות רוחב הפס באפליקציות שלהם עולות. TR הינו מחבר ה – multicoax המהיר ביותר בעולם. הממשק הוא של לחיצה ישירה אל המעגל המודפס ללא צורך במחבר נגדי בצד של המעגל.

תורגם ע”י: עדי פלג, מנכ”ל מ.ט.י סאמיט אלקטורניקה בע”מ