מעגל חוג נעול מופע (phase-locked loop – PLL) הוא מערכת משוב המשלבת מתנד מבוקר מתח (VCO) וגלאי מופע כך שאות המתנד עוקב אחר תדר מיושם או מופע אות מווסת עם התדר וה- phase הנכונים. משתמשים במערכות PLLs כאשר יש צורך ליצור תדרי פלט יציבים הגבוהים יותר מאותות תדרים נמוכים קבועים או כאשר יש צורך בשינויי תדר מהירים. השימוש האופייני הוא ב- high frequency telecommunication וטכנולוגיית מדידה למימוש מסננים, אפנון ו- demodulation, כמו גם לסינתזת תדרים.

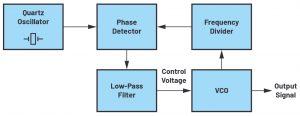

איור 1: תרשים של חוג נעול מופע (PPL)

איור 1 מציג תרשים זרימה של סינתיסייזר תדרים מבוסס PLL. ה- VCO מפיק את אות הפלט. זה נשמר בתדר ה- setpoint בעזרת ה- PLL וננעל לתדר הרפרנס. תדר הרפרנס מסופק לרוב על ידי מתנד קוורץ מאד מדויק. מחלק תדרים מסופק בנתיב המשוב של מעגל ה- PPL בקדמת גלאי הפאזות כדי להפחית את תדר ה- VCO על ידי גורם מתכוונן.

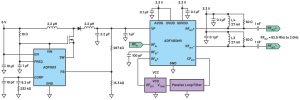

ה- VCO מכיל אלמנט כיוונון ניתן להתאמה, כמו varactor diode עם קיבול המשתנה בהינתן מתח הקלט. מכאן שמעגל PLL הוא סוג של מערכת בקרת משוב עבור ה- VCO. מתח הקלט או הבקרה הנדרשים ל- VCO הוא לרוב גבוה יותר ממתח האספקה הזמין למעגל ה- PLL. מתח האספקה הוא לרוב V 3.3 או V 5, בעוד VCOs עשויים לדרוש מתח של יותר מ- V20 בהתאם לתדר המבוקש. ניתן להשתמש ב- VCOs עם טווח כוונון רחב יותר על מנת לייצר מגוון רחב יותר של תדרים. דוגמה למעגל מפושט התומך ב- VCOs בטווח ה- gigahertz מוצג באיור 2.

איור 2: מעגל מפושט של אספקת משאבת טעינה במתח גבוה עבור ה- .ADF4150HV

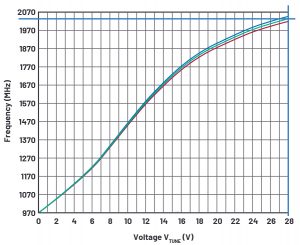

ניתן להשתמש ב- DCYS100200-12 של Synergy Microwave Corporation כ- VCO. זה מאפשר תדר של GHz 2 ב- V28 (VTUNE), כפי שניתן לראות בתרשים המופיע באיור 3.

ישנן מספר אפשרויות להפקת מתח בקרה גבוה. אחת האפשרויות היא במסנן לולאה פעיל, המורכב בעיקרו ממגבר במהירות גבוהה ומסנן low-pass המשנה את פעימות הפלט מגלאי ה- phase (CPOUT) למתח dc נקי. אפשרות נוספת כחלופה לכך היא שימוש בסינתיסייזר בתדר PLL עם משאבת טעינה משולבת, כגון ADF4150HV תוצרת Analog Devices, Inc. (ADI), שאינו מצריך מסנן לולאה פעיל נוסף. למרות ששני פתרונות אלו דורשים אספקת מתח גבוהה, ניתן להפחית את מספר הרכיבים בעזרת ADF4150HV. בנוסף ניתן להימנע מעיוותי ורעשי phase הנגרמים על ידי מגבר המסנן הפעיל. יתר על כן, ה- ADF4150HV מאפשר הטמעת סינתיסייזרים של תדר PLL עם fractional-N או integer-N. לפיכך, ניתן לחלק את תדר ה- VCO ב- 1, 2, 4, 8 או ,16 כך שמתאפשרים תדרי פלט עד למינימום של MHz 31.25.

איור 3: מתח בקרה לעומת תדר של ה- DCYS100200-12.1

ניתן להפיק את המתח הגבוה הדרוש למשאבת הטעינה המשולבת של ADF4150HV באמצעות dc-to-dc boost converter ADP1613 מבלי שיהיה צורך להתפשר על ביצועי ה- PLL. ה- ADP1613 הוא ווסת מיתוג יעיל עם power transistor משולב להשגה קלה של מתחי קלט של עד V 20. ניתן להשיג מתחי קלט גבוהים יותר גם באמצעות רכיבים חיצוניים נוספים, בייחוד באמצעות power transistor חיצוני. ניתן להתאים את תדר המיתוג של ה- ADP1613 בטווח שבין kHz 650 ל- MHz 1.3. זה מוביל לתגובה ארעית טובה יותר ולסינון רעשים פשוט. באופן כללי, מומלץ לבחור בתדר הגבוה מ- MHz 1 על מנת שאפשר יהיה להפחית את רעש המיתוג באמצעות מסנן לולאת PLL.

מעגל סינתיסייזר התדר PLL עם ADF4150HV מציע פונקציית PLL עם ultrawideband באמצעות השימוש ב- RF divider משולב. זה מאפשר כיסוי תדרים בטווח של MHz 62.5 עד 2 GHz. בעזרת שימוש באותו עיצוב חומרה של PLL, ניתן להפיק תדרים שונים עבור מגוון פלטפורמות חומרה שונות בתוך המערכת. אולם, אם נדרש עיצוב לסוגי VCO שונים, יש הגיון לשלב בתכנון מסנן מתאים. כך ניתן להבטיח את אמינות הפעולה של ה- PLL. עבור טווח ההתאמה הרחב יחסית של תדר הפלט ועוצמת הפלט הגבוהה המשויכת אליו, נדרש גם מבנה מסנן קטן בכל אחת מפלטי ה- RF של ה- ADF4150HV. משרן 27 nH במקביל ל- 50 Ω resistor מציעים התאמה טובה לתדרים של עד GHz 3. ה- resistor מספק השהיית פלט מוגדרת. השראות נמוכות יותר יובילו להתרחבות של frequency band לטווחים נמוכים יותר.

כיום, ישנם גם פתרונות משולבים לטווחי תדרים גדולים יותר (כלומר עבור PLLs, מסננים ו- VCOs) במארז אחד. אולם זה יכול להוביל לצימוד בלתי רצוי בגלל קירבת המרחק של הרכיבים השונים זה לזה. תכנון דיסקרטי וההפרדה הפיזית הנובעת מכך ממזערים את הסיכון הזה.

גם כלי הסימולציה ADIsimPLL™ של PLL frequency synthesizer מספק גם תמיכה מועילה בפיתוח בלוקים פונקציונליים של HF ושרשראות אות HF מתוכננות. זה מאפשר למתכננים לדמות בקלות יחסית את כל האפקטים הלא-לינאריים החשובים שעלולים להשפיע על יכולות הביצועים של ה- PLL; לדוגמה, הסטה לא רצויה מתהליך סינתזת התדרים (spurious frequencies).

מקורות

1 “Voltage Controlled Oscillator Surface-Mount Model: DCYS100200-12.” Synergy Microwave Corporation, October 2014.

“Circuit Note CN-0228: Single-Supply Power a 28 V, High Voltage Phase-Locked Loop (PLL) Synthesizer.” Analog Devices, Inc., June 2014.

אודות המחבר

תומס ברנד (Thomas Brand), החל את הקריירה שלו בחברת Analog Devices בשנת 2015 במינכן, כחלק מעבודת התזה ללימודי תואר שני. לאחר סיום לימודיו הוא לקח חלק בתכנית הלימודים בחברת Analog Devices. בשנת 2017, הוא הפך למהנדס יישומי שטח. תומס מספק תמיכה ללקוחות תעשייתיים גדולים במרכז אירופה ומתמחה בתחום של Ethernet תעשייתי. הוא למד הנדסת חשמל באוניברסיטת Cooperative Education ב- Mosbach והשלים מסלול לימודי מכירות בינלאומיות במסגרת לימודי התואר השני שלו ב- University of Applied Sciences ב- Constance. ניתן ליצור איתו קשר בכתובת: thomas.brand@analog.com.