בעקבות הרחבה מהירה של אפשרויות המוצר של SiC, האתגר הבא בתעשייה הוא פישוט של תהליך התכנון עבור משתמשי הקצה. מפתחי מערכות חשמל זקוקים לפתרונות הוליסטיים שאינם מטפלים רק באלמנטים עיצוביים טיפוסיים באופן פרטני אלא מכירים בחשיבות האינטראקציות שלהם. במילים אחרות, על ספקי SiC שאפתניים לא רק להפגין את הביצועים והקשיחות של טכנולוגיית ה-SiC MOSFET שלהם, הם חייבים לסייע באתגרים תכנוניים באמצעות הצעה של אריזות כוח בעלות השראות נמוכה ומנהלי התקני מעגל מתוחכמים יותר כדי לתמוך ולהגן על פרמטרים של המערכת ולכוונן אותם. התחשבות בשלושת החלקים המרכזיים הללו היא ערובה לפישוט ההערכה והעיצוב עבור אלה המעוניינים לנצל את השיפורים שמפריעים ברמת המערכת, דבר שמתאפשר עם SiC.

SiC MOSFET חזק וחסין

ניתן לטעון כי החולייה הקריטית ביותר בשרשרת מערכות החשמל, SiC MOSFETs חייבים להפגין חוסן בכמה אזורי מפתח שבהם הם היו פגיעים באופן מסורתי. כמו MOSFETs מסיליקון, גם הם התמודדו עם בעיית הפגמים החיצוניים כגון זיהומים, מצבי טעינה ופגמים אחרים בחומר בקרבת ממשק תחמוצת-מוליכה למחצה, אשר מגבירים מגוון של מנגנוני חוסר יציבות והפחתה בפעילות. ביטול הסיכונים הללו דורש כי SiC MOSFETs בדרגה הייצור יפגינו מתח סף יציב, תחמוצת מעגל אמינה, דיודת גוף פנים חזקה וקשיחות בתנאי קריסה. יש לאמת כל מאפיין באמצעות בדיקות הסמכה כיוון שיציבות הפרמטרים ואורך החיים עשויים להשתנות באופן דרמטי בין ספק אחד למשנהו.

כדי לבדוק את יציבות מתח הסף (Vth) של SiC MOSFET, מקובל להפעיל לחצי מקדם מעגל חיוביים (p-HTGB) ושליליים (n-HTGB) בטמפרטורה גבוהה על מספר משמעותי של מכשירים מבחינה סטטיסטית ופשוט להשוות את ה-Vth לפני הלחץ ואחריו. לדוגמה, p- ו- n-HTGB בוצעו בערכות עצמאיות של שישים וארבעה 1200 V SiC MOSFETs במשך 1000 שעות. השינוי הממוצע שנצפה ב- Vth היה 59.6+ מיליוולט לאחר p-HTGB ו-22.8- מיליוולט לאחר n-HTGB. ברמת יציבות זו, למפתחים יש צפי לסף המתח שסביבו הם יכולים לבצע בחירות עיצוב הדוקות וארוכות טווח יותר.

תחמוצות מעגל בעלות אמינות גבוהה הן קריטיות לכל היישומים, במיוחד עבור אלה הדורשים חיי שירות ארוכים. כדי לקבוע את האמינות של תחמוצת מעגל ה-SiC MOSFET הנתונה, נערכו מדידות מטען לפירוק (QBD) על שלוש אוכלוסיות המונות 1200 V SiC MOSFET. כל התקלות שנצפו היו מהותיות, דבר שמעיד על רמת בגרות גבוהה של התהליך. שיעורי כשל בזמן (FIT) ושעת הכשל הממוצעת (MTTF) חושבו באמצעות אוכלוסייה רחבה יותר של 192 מכשירים. עבור p-HTGB, נמצא כי הערכים הם 20 ו-5,618 שנים; עבור n-HTGB, ה-FIT היה 93 עם MTTF של 1,233 שנים. משתמשי קצה אמורים לשאוב מכך עידוד משום שתוצאות אלה תואמות את דיווחי התפלגות הדיאלקטרית התלויה בזמן (TDDB) מצד מספר ספקים.

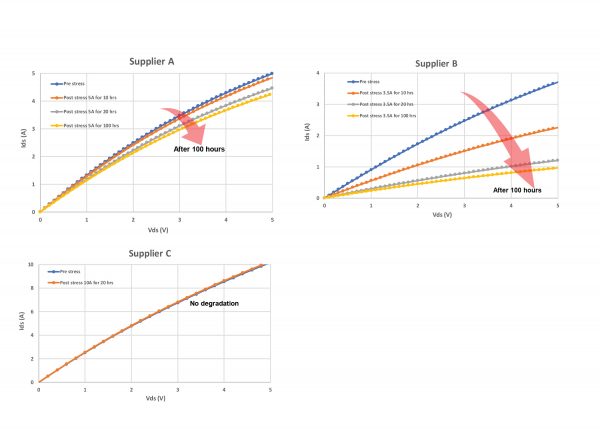

תופעה של הפחתה דו קוטבית בצמתי p-n SiC נחקרה רבות. אם הדבר יתרחש בדיודת גוף של SiC MOSFET, ניתן יהיה לראות התגברות הן במצב ההתנגדות והן בנפילת המתח על פני הדיודה במהלך ההולכה הנוכחית (מתגלה על ידי סחף מזיק במאפייני הפלט של הרבע השלישי). למרבה המזל חומרי SiC MOSFET הבשילו, וצפיפותם של פגמים בגבישים שהיו קודם לכן פחתה בחומרים בדרגת הייצור. עם זאת, יש לבחון את ה-SiC MOSFETs של כל ספק. אוניברסיטת אוהיו השוותה לאחרונה הפחתה בדיודות גוף לאחר 100 שעות של מתח בזרם מלא (VGS = -5 V) ב-1200 V SiC MOSFETs ממספר ספקים, וחשפה פערים משמעותיים בהתנגדות לאחר מצב לחץ במצב מצב פעיל. רק ספק C לא הראה הפחתה (איור 1). נתונים משלימים לרביע השלישי על אותם מכשירים אישרו את נוכחותה (או היעדרם, עבור ספק C) של של הפחתה בדיודת הגוף.

איור 1. נתונים מהרביע השלישי מראים שרק SiC MOSFET מספק C לא חווה הפחתה בדיודת הגוף. מקור: ד"ר אננט אגארוואל וד"ר מינסוק קנג, אוניברסיטת אוהיו.

מאפיין חשוב נוסף להערכה הוא קשיחות בעת קריסה, שמתבצעת באמצעות מיתוג אינדוקטיבי לא מהודק (UIS). ה-MOSFET מוזן בנחשול מתח כשהוא במצב כבוי, דבר שמאלץ את כל הזרמים לקריסה בהיקף הפיסה, מכיוון שערוץ ה-MOS אינו משופר. הדבר שונה מבדיקת עמידות לטווח קצר, שבו ה-MOSFET במצב ON והזרם מתפזר בצורה אחידה יותר על פני כל השטח הפעיל של המכשיר. כדי לחקות מקרוב את תנאי השדה בחיים האמיתיים, ה-SiC MOSFETs נתונים לפולסים חוזרים ונשנים של UIS (R-UIS); היציבות הפרמטרית ושלמות התחמוצת מושווים לפני ואחרי 100,000 פולסים חוזרים ונשנים בזרם מדורג של שני שליש (לכל MIL-STD-750). VBR, Vth ו-VF של דיודת הגוף אינם מושפעים מ-R-UIS, דבר שמעיד על חסינות מעולה לקריסה.

אריזות כוח בעלות השראות נמוכה

בעזרת הביטחון שנוצר ב-SiC MOSFET, היצירה האינסטרומנטלית הבאה של פתרון המערכת הכולל של SiC היא חבילת כוח ממוטבת. חבילת מודול רב שבבית יעילה חייבת לאפשר למעצבים למנף את היתרונות של SiC ולא לעכב אותם.

ישנן דרישות רבות שיש לקחת בחשבון. מכיוון שפיסות ה-SiC MOSFET קטנות יחסית, יש להקביל רבות מהן כדי להשיג התנגדות נמוכה במצב פעיל. כמו כן, פיסות ה-MOSFET המקבילות חייבות לעבור באותו תזמון ושיתוף זרם אחידים, כלומר להבטיח סימטריה וגם השראות נמוכות באמצעות תוכניות חיבור לפיסה.

דוגמה לכך היא חבילת ה-SP6LI של Microchip שמכניסה רק 2.9 ננו-אנרי (nH) של השראות תועות ללולאת החשמל, בהשוואה ליותר מ-20 nH של השראות טפיליות בחבילות מודול סטנדרטיות. השראות לולאת החשמל מופחתות באמצעות סידור חיבורי קישור DC בסרגלי פסים המוגדרים כקווי רצועה. חיבורי מצע מופצים באופן סימטרי וקרובים ככל האפשר לפיסת המוליכים למחצה. ביחס ללולאת מעגל המקור, משבצות של נגדי מעגלים עצמאיות של סדרות משמשות לכל אחד משנים עשר חללי הפיסה הזמינים במצבי המתג הגבוהים הנמוכים כדי למטב את העיתוי והשיתוף הנוכחיים. נגדי המעגל העצמאיים מפחיתים השראות טפיליות שמוכנסות ללולאת מעגל המקור, ומגנים מפני אירועי קטסטרופלי תוך צמצום הפסדי מיתוג.

טכנולוגית מנהלי התקני מעגל חכמה וגמישה

החלק הקריטי השלישי הנדרש לפתרון כולל של מערכת SiC הוא שליטה. שוב, יכולת המיתוג המהירה של SiC MOSFETs מציבה מערכת לא ממוטבת בסיכון לכשל EMI ועליות מתח זמניות. דרושה רמה חדשה של טכנולוגיית מנהלי התקן המעגל המאפשרת למתכנן לתפעל דינמיקת מיתוג ולהגיע לתמורות מיטביות. יתרה מזאת, על מנהלי התקן המעגל לספק איתור ותגובה מהירה לתנאי מתח, מכיוון של-SiC MOSFETs יש זמני עמידה קצרים יותר בהשוואה לרוב ה-IGBTs מסיליקון.

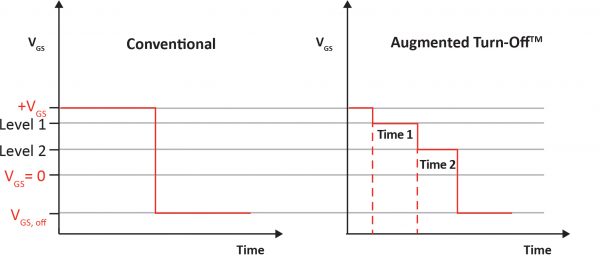

באמצעות טכניקה מוגנת בפטנט המכונה מיתוג מוגבר, פתרונות מנהלי התקן המעגל הדיגיטליים האחרונים מאפשרים השהיה ב-VGS הביניים שצוין על ידי המשתמש למשך הזמן הרצוי כדי לפרוק את קיבוליות המילר לפני המשך ל-VGS שברקע (ראו איור 2). הדבר מנוגד לגישות מסורתיות שלוקחות VGS ישירות מרמת מצב פועל לרמת מצב כבוי, ואינם מציעים למעצב נתיב מילוט מהמלכודות האחרות של המערכת, כגון השראות טפיליות של הכבל המשמש לחיבור העומס. אכן, תמורות דרמטיות בין מעבר מתח ויעילות עשויות להתממש בעזרת שינויים קלים בפרופיל ה-Augmented Switching (רמות VGS וזמן השהייה).

איור 2: מנהלי התקני מעגל דיגיטלי שעושים שימוש בגישה מיתוגית מוגברת מבצעים משימה פשוטה וישירה לזיהוי נקודות התכנון האופטימליות ולכימות של ערכן בפני בעלי העניין.

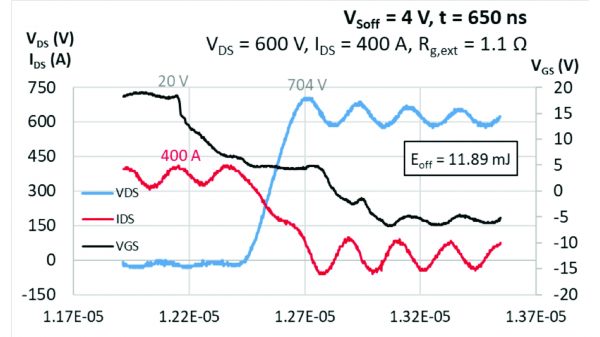

איור 3 מציג צורות גל כבויות באמצעות שני פרופילים מוגברים למיתוג ומודול SiC MOSFET של 1200 V במארז D3 (106 מ"מ x 62 מ"מ x 31 מ"מ). ניתן לשים לב שבחירת VGS ביניים נמוכה יותר מפחיתה הפסדי מיתוג כאשר היעילות היא בראש סדר העדיפויות, ואילו השימוש ב-VGS גבוה יותר מעכב את VDS מגביר ומרכך את התנודות של שלוש צורות הגל. בעזרת הכלי המסופק עבור תצורת התוכנה ניתן לכוונן את הגדרות מנהל ההתקן במעגל בכל השלבים לאורך נתיב הפיתוח בלחיצת עכבר, בניגוד לשעות שביליתם בהחזקת מלחם.

איור 3. צורות גל כבויות שממחישות את ההשפעות של מיתוג מוגבר במודול SiC MOSFET.

מנהלי התקנים למעגל דיגיטלי יכולים גם להציע אינטליגנציה משופרת. לדוגמה, ניתן להשתמש בהם כדי להפעיל פרופיל כיבוי שונה לחלוטין במקרה של תקלות כדי להבטיח את הדרך המעבר הבטוח ביותר. שילוב שיטות AS בהגנה על קצר חשמלי מחזק את השימוש ב-Rg, נמוך, כמו גם את הנחיית ה-MOSFET למעבר רך ומבוקר יותר למצב כבוי עם סבירות מופחתת לקריסה. תכונות הניתנות להגדרה נוספת כוללות אמצעי אבחון בזמן אמת, כגון מתח קישור DC וניטור טמפרטורות

ככל שמעצבי אלקטרוניקה חשמלית עוברים מ- IGBTs סיליקון ל-SiC MOSFETs, הם מסתמכים יותר ויותר על ספקי רכיבים שיספקו את האלמנטים הקריטיים להם הם זקוקים בכדי ליצור פתרונות מערכת כוללים. הדבר כולל SiC MOSFET עם חוסן מוכח, חבילת כוח עם השראות נמוכה במיוחד, ומעמד חדש של מנהלי התקני מעגלים חכמים שנבנו כדי להקל על האופטימיזציה. כל אחד מהם הוא תנאי מקיף לייעול מסע העיצוב של SiC מהערכה ראשונית דרך פריסה בשדה.