בראיון זה מתאר סרי סאמוונדם (Sri Samavedam), סגן נשיא בכיר טכנולוגיות CMOS ב־imec, מגמות חשובות בתעשיית המוליכים למחצה. כמו כן, הוא מסביר כיצד תוכניות המחקר והפיתוח של imec בתחום טכנולוגיות ה־CMOS עוסקות במציאת פתרונות לאתגרים האלו כדי לקדם את התעשייה לעבר מימוש טכנולוגיות הדור הבא.

מהם החידושים האחרונים בתחום מזעור שבבי ה־ CMOS שנראה בשוק בשנים הקרובות?

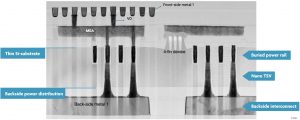

השימוש בגב פרוסת הסיליקון להזנת ההתקן האלקטרוני הוא פיתוח שיאפשר את קפיצת המדרגה הבאה בביצועי השבבים. שכבות המתכת המסורתיות בחזית פרוסת הסיליקון ימשיכו לשמש לניתוב אותות, בעוד ששכבות המתכת בגב פרוסת הסיליקון ישמשו להזנת החשמל. הפרדת הזנת החשמל ממערכת ניתוב האותות מאפשרת להקטין את מפל המתח במעגל (וכך לשפר את הביצועים) ואת צפיפות הניתוב בחזית השבב. אינטל הכריזה על כוונה לעבור לארכיטקטורה הזאת לייצור התקנים במבנה ננו־משטחים (Nanosheets) בתהליך 2 ננומטר.

תמונת מיקרוסקופ אלקטרונים חודר (TEM) של טרנזיסטורים מסוג FinFET בחזית וגב פרוסת הסיליקון.

הארכיטקטורה שתחליף את מבני ה־Nanosheet וה־Forksheet תהיה מבוססת על טרנזיסטורים מסוג Complementary FET (או CFET בקיצור; בתרגום חופשי לעברית: טרנזיסטור תוצא שדה משלים) שבהם צמתי ה־PN נערמים זה על גבי זה בתהליך ייצור מורכב. קיימות כמה ארכיטקטורות אפשריות למימוש טרנזיסטורים מסוג CFET, וכיום אנחנו נמצאים בשלבים המוקדמים של מציאת הארכיטקטורה היעילה והמבטיחה ביותר מביניהן.

קיימות כמה ארכיטקטורות אפשריות למימוש טרנזיסטורים מסוג CFET, וכיום אנחנו נמצאים בשלבים המוקדמים של מציאת הארכיטקטורה היעילה והמבטיחה ביותר מביניהן.

עבור המטליזציה בגב השבב, תוחלף שיטת השיקוע Damascene הכפולה של נחושת בתהליך איכול מתכת, ליצירת פסים קטנים מ־20 ננומטר עם יחס צירים גבוה. עיקר המאמצים שלנו מתמקדים באיכול מתכת ישיר של רותניום. כדי להקטין את ההתנגדות, יש להגדיל את יחס הצירים של הרותניום לצד שימוש בכיסי אוויר להקטנת השפעת הקיבול. השינויים האלה יבטיחו כי מפת הדרכים הטכנולוגית למימוש מערכת הזנת החשמל בגב השבב תאפשר את המשך מזעור השבבים כמה דורות קדימה.

באילו מגמות אתה מבחין בתעשייה על רקע ההאטה בקצב מזעור השבבים?

זה לא סוד שהמשך מזעור המעבדים ושבבי הזיכרון הופך למאתגר יותר בכל דור. השיפורים במעבר מדור ייצור אחד למשנהו קטנים בהתמדה, בעוד שעלות הייצור רק ממשיכה לעלות בשל מורכבות התהליך. בצד תכנון השבבים, אחת המגמות המרכזיות היא מעבר לשבבים ייעודיים ליישומים מסוימים כמו למידת מכונה, גרפיקה, עריכת וידאו והתמקדות גדולה יותר באופטימיזציה של התוכנה לחומרה כדי לשפר את ביצועי המערכת כולה.

בתוך כך, נעשה ניסיון לזהות טכנולוגיות לצמצום צווארי בקבוק במערכת, כמו תופעת חומת הזיכרון (לצמצום הפער בין מהירות המעבד למהירות הזיכרון תוך שמירה על צריכת אנרגיה נמוכה), צריכת האנרגיה ופליטת החום (למניעת האטה בביצועי המערכת) ותקשורת (כיצד להבטיח שתשתיות התקשורת החוטית, האלחוטית והאופטית יצליחו להתמודד בהצלחה עם כמויות המידע הגדלות בהתמדה), במקום להסתמך על טכנולוגיות כלליות שכבר קיימות בשוק.

תמונה: תמונת מיקרוסקופ אלקטרונים חודר (TEM) של טרנזיסטורים מסוג FinFET בחזית וגב פרוסת הסיליקון.

קרדיט: IMEC

בתוך כך, נעשה ניסיון לזהות טכנולוגיות לצמצום צווארי בקבוק במערכת, כמו תופעת חומת הזיכרון (לצמצום הפער בין מהירות המעבד למהירות הזיכרון תוך שמירה על צריכת אנרגיה נמוכה), צריכת אנרגיה ופליטת חום (למניעת האטה בביצועי המערכת) ותקשורת (כיצד להבטיח שתשתיות התקשורת החוטית, האלחוטית והאופטית יצליחו להתמודד בהצלחה עם כמויות המידע הגדלות בהתמדה), במקום להסתמך על טכנולוגיות כלליות שכבר קיימות בשוק.

בתחום המחשוב עתיר הביצועים, כבר קיימות דוגמאות כמו טכנולוגיית V-cache של AMD והשימוש בגשר מסיליקון לחיבור שתי יחידות עיבוד נפרדות במערכת על השבב M1 Ultra של אפל שבהן נעשה שימוש במבנה תלת־ממדי כדי לקרב את זיכרון ה־SRAM למעבד. מגמה נוספת היא השימוש בטכנולוגיות 3D ו־2.5D לשילוב שבבים אלקטרוניים ופוטוניים על אותו מצע סיליקון, כדי להקטין את ההתנגדות החשמלית הטפילית ברוחבי הפס ההולכים וגדלים במערכות תקשורת אופטית, כשקיימות אפשרויות שונות ליצירת חיבורי 3D ו־2.5D בהתאם לצפיפות החיבורים, העלות ומורכבות התהליך. אתגר נוסף הוא שעל הציוד, שיטות הייצור והכלים לתכנון מעגלים משולבים (EDA) להבשיל לרמה שתאפשר ייצור מסחרי שיאיץ את אימוץ הטכנולוגיות החדשות האלו.

כיצד נערכת imec למגמות העתידיות האלו?

תוכנית אופטימיזציית טכנולוגיות תכנון השבבים (DTCO) של imec עוסקת במציאת הארכיטקטורות היעילות ביותר עבור שבבי עיבוד, שבבי זיכרון ושבבי אחסון תלת־ממדיים, במטרה לפתח ערכות תכנון תהליך (PDK) שישמשו כבסיס לתהליכי ייצור עתידיים. בתוכנית אופטימיזציית טכנולוגיות המערכת (STCO) אנחנו משתמשים בערכות לתכנון התהליך (PDK) האלו כדי למצוא פתרונות לאתגרים, כמו תופעת חומת הזיכרון ופליטת החום שמשפיעים על ביצועי המערכת כולה. כך לדוגמה, אנחנו עובדים על מבנים פנימיים שונים של שבבים תלת־ממדיים כדי להתאימם ליישומים מסוימים, מבצעים ניתוח תרמי לבדיקת פתרונות קירור שונים וחוקרים את שימוש בזיכרון היברידי.

כדי לקדם את הבשתלן של טכנולוגיות שבבים תלת־ממדיים, אנחנו עובדים בשיתוף פעולה צמוד עם ספקי ציוד מובילים ועם Cadence, כדי לפתח כלים לתכנון מעגלים משולבים (EDA) הנחוצים לחלוקה פנימית של מערכות על שבב תלת־ממדי והתאמתן ליישומים מסוימים.

אתה יכול לתת כמה דוגמאות לתחומים מבטיחים בתחום טכנולוגיות ה־CMOS שבהם עוסק המחקר והפיתוח ב־imec?

בתחום השערים הלוגיים, אנחנו ממשיכים לחקור ולבדוק רכיבים ושיטות שונים למימוש התקנים אלקטרונים על בסיס טרנזיסטורים מסוג CFET שצפויים לאפשר מבנה תא 4T. כמו כן, נרשמה התקדמות בשילוב כיסי אוויר בפסי מתכת בעלי יחס צירים גבוה בגב השבב, לצורך שליטה על ערכי ההתנגדות והקיבול שתאפשר את המשך מזעור השבבים דורות קדימה. בתחום המחשוב הקוונטי, אנחנו עובדים על הקטנת רעש המטען בהתקנים עם קיוביטים מבוססי ספין מסיליקון לשיפור מהימנות הפעולות המבוצעות על קיוביטים וכך לשפר גם את אמינות החישוב הקוונטי.

כמו כן, נרשמה התקדמות בשילוב כיסי אוויר בפסי מתכת בעלי יחס צירים גבוה בגב השבב, לצורך שליטה על ערכי ההתנגדות והקיבול שתאפשר את המשך מזעור השבבים דורות קדימה.

ככל שקצבי הנתונים המועברים במערכות תקשורת אופטיות ממשיכים לגדול, כך מתגבר הצורך להשתיל את המעגלים האלקטרוניים והפוטוניים קרוב יותר זה לזה על אותו מצע סיליקון, כדי לצמצם הפסדים טפיליים. אנחנו מפתחים רכיבים חדשים שיאפשרו את השילוב הזה.

במסגרת תוכנית שבבי הזיכרון הדינמי, אנחנו ממשיכים לשפר את ביצועיהם ואמינותם של התקני IGZO (אינדיום־גליום־אבץ־חמצן), שלהם יהיה תפקיד מרכזי בהמשך מזעור שבבי זיכרון DRAM. תוכנית שבבי האחסון שלנו ממשיכה להתקדם לפי מפת הדרכים שתאפשר את המשך מזעור שבבי זיכרון ההבזק התלת־ממדיים בטכנולוגיית NAND ליישומי אחסון.

כיצד תורמת imec לשמירה על הסביבה ולמאבק במשבר האקלים?

imec נוקטת בגישה מקיפה והוליסטית לקידום קיימות. אנחנו מתכננים להקטין את טביעת הרגל הפחמנית של פעילותנו בשיעור של 65% עד שנת 2030, ולפי שעה עומדים בלוחות הזמנים להשגת היעד הזה. כמו כן, אנחנו מעודדים איזון עבודה־חיים בריא, מטפחים תרבות של בטיחות וכל פעילות המחקר שלנו נעשית לפי היעדים לפיתוח בר־קיימא של האו"ם. מאמצי המחקר והפיתוח שלנו עוסקים גם בפתרונות לעידוד מעבר משק האנרגיה למקורות של אנרגיה מתחדשת, כמו דלק מימן ומערכות סולאריות.

בשנה שעברה, השקנו את תוכנית מערכות וטכנולוגיות בנות קיימא לייצור מוליכים למחצה (SSTS), במטרה למדוד את פליטת גזי החממה הנוצרים בתהליך הייצור של מעבדים, שבבי זיכרון ושבבי אחסון ולהקטינה.

בשנה שעברה, השקנו את תוכנית מערכות וטכנולוגיות בנות קיימא לייצור מוליכים למחצה (SSTS), במטרה למדוד את פליטת גזי החממה הנוצרים בתהליך הייצור של מעבדים, שבבי זיכרון ושבבי אחסון ולהקטינה.

מטרתנו היא לרתום את כל תעשיית המוליכים למחצה למאבק במשבר האקלים העולמי. שותפי טכנולוגיה מובילים כמו אפל, אמזון, מיקרוסופט, ASM, ASML, Kurita, Screen ו־Tokyo Electron כבר הצטרפו לתוכנית ואנחנו מקווים להכריז בהמשך על הצטרפותם של יצרני ציוד, יצרניות שבבים ויצרני מערכות נוספים. אנחנו עובדים ביחד עם SEMI (מועצה מייעצת בתחום הקיימות) על שיתוף לקחים ושיטות עבודה מומלצות, כדי לעודד את אימוצם על ידי חברות מובילות נוספות בתעשייה.

סרי סאמוונדם (Samavedam Sri)

סגן נשיא בכיר טכנולוגיות CMOS ב־ imec. קרדיט צילום: IMEC

About Sri Samavedam

Sri Samavedam is senior vice president of CMOS technologies at imec since August 2019. His responsibilities include programs in logic, memory, photonics and 3D integration. Prior to that, he was senior director of technology development at GlobalFoundries in Malta, NY, where he led qualification of 14nm FinFET technology and derivatives into volume production and early development of 7nm CMOS. He began his research career at Motorola in Austin, TX, working on strained silicon, metal gates, high k dielectrics and fully-depleted SOI devices. He holds a Ph.D. in Materials Science and Engineering from MIT and a masters from Purdue University.

קרדיט תמונת כותרת: IMEC