Haim Cohen, Freescale Semiconductors

Haim Cohen, Freescale Semiconductors

ככל שחוק מור המשיך להגביר את הביצועים והאינטגרציה של מעבדים כך הצורך בכבלי חיבור (interconnects) בעלי מהירות גבוהה יותר המשיך לצמוח אף הוא. כבלי החיבור של ימינו מפגינים בדרך כלל מהירויות של החל מ-1 ועד 40 ג'יגה בתים לשנייה, ויש להם מפות דרכים המובילות למאות ג'יגה בתים לשנייה.

במירוץ למהירויות גבוהות יותר ויותר של כבלי חיבור, לעתים קרובות לא דנים בסוגי הטרנזקציות הנתמכים, זמן האחזור של התקשורת, התקורה של התקשורת, ואילו סוגי טופולוגיות יכולים להיתמך בקלות.

אנו נוטים לחשוב שכל כבלי החיבור נוצרו שווים ובעלי גורם איכות (figure of merit) המבוסס אך ורק על רוחב פס בשיא. אך המציאות שונה למדי. למרות שיש צורות שונות של מעבדים הממוטבים ליישומים כלליים, יישומי עיבוד אותות, גרפיקה ותקשורת, כבלי חיבור גם תוכננו ועברו אופטימיזציה לפתרון של בעיות קישוריות שונות.

בדרך כלל כבל חיבור יפתור את הבעיות שעבורן תוכנן ביעילות רבה, וניתן להשתמש בו גם לפתרון בעיות אחרות, אך הוא יהיה פחות יעיל ביישומים אלה. בהקשר זה, יועיל לסקור שלושה כבלי חיבור חשובים. כבלי חיבור אלה הם ®PCI Express בגרסת Gen 2 ו-Gen 3, אתרנט בגרסת ה-10 ג'יגה בתים הפופולארית, וטכנולוגיית ®RapidIO מדור שני ומדור שלישי, שהושקה בשנת 2008.

כל אחת מהטכנולוגיות הללו עברה לשכבה פיזית עם ממשק SerDes מרובה-נתיבים, ומשתמשת בקידוד קו 8B/10B או בקידודי קו יעילים יותר, כגון קידוד קו 64B/66B במהירויות גבוהות יותר. בעוד ש-PCI Express ו-RapidIO מציעים ממשקים רחבים יותר מ-4 נתיבים, ממשקים רחבים יותר לא ישמשו בדרך כלל בלוחות אם או במחברי סיבים או כבלים. תקן Gen 3 RapidIO מרחיב את סכימת ה-64B/66B של תקן אתרנט KR עם היפוך סיביות בקוטביות מיוחדת (64B/67B) המבטיח המשך איזון DC של זרם הסיביות המשודר.

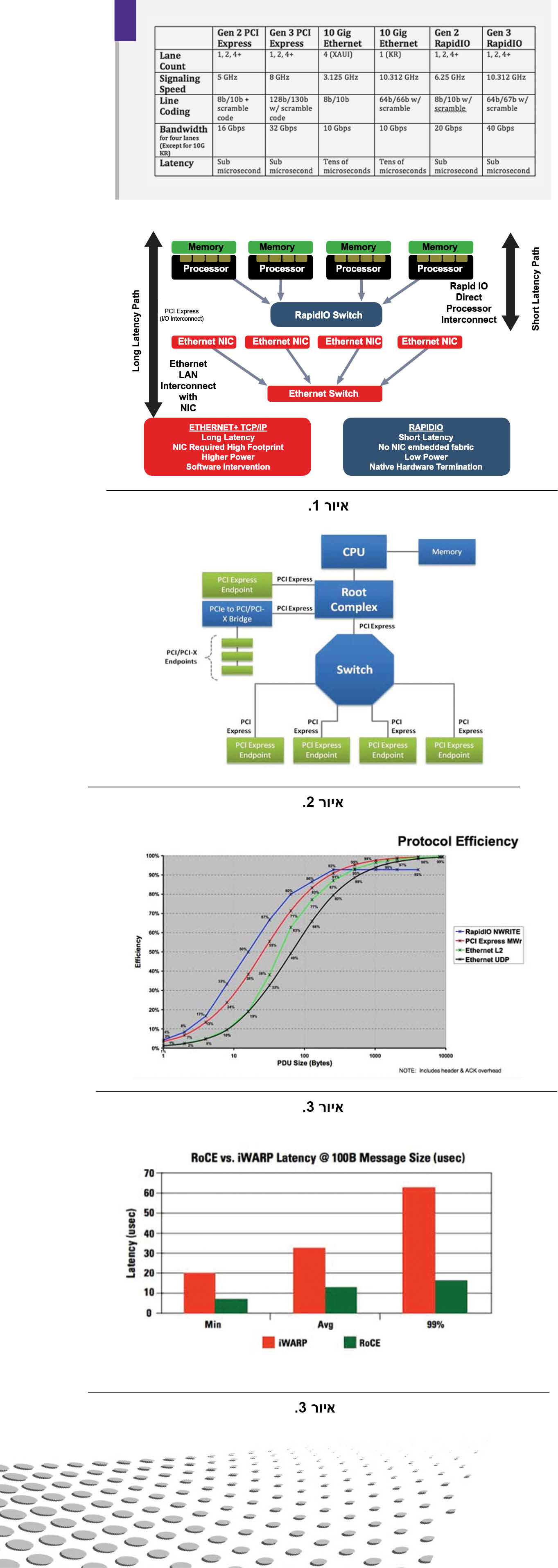

הטבלה הבאה מציגה את רוחב הפס האופייני ואת תצורות הנתיבים עבור PCI Express, RapidIO ואתרנט 10 ג'יגה-סיביות, כפי שהם משמשים ביישומי קישוריות מעבדים.

מאמר זה יתמקד לא ברוחבי הפס הגולמיים של טכנולוגיות כבלי חיבור, אלא ביכולות פרוטוקול אינהרנטיות, טופולוגיות נתמכות ויעדי תכנון זמן אחזור לכל אחד מכבלי החיבור הללו. כך נבין טוב יותר היכן הגיוני להשתמש בכל טכנולוגיה.

טרנזקציות וטופולוגיה של PCI Express

PCI Express תוכנן, ב-2003, לחבר התקנים היקפיים, בדרך כלל התקנים משניים כגון כרטיסי רשת אתרנט ושבבים גרפיים, למעבד מארח ראשי. הוא לא נועד לשמש ככבל חיבור בין מעבד למעבד, אלא כגרסה טורית של אפיק PCI.

PCI הוא ראשי תיבות של Peripheral Component Interconnect (חיבור רכיבים היקפיים). PCI Express שומר על אותו דגם תכנות וגישה לקישוריות. מבחינה טופולוגית, PCI Express יכול לתמוך בהיררכיה של אפיקים עם אירועים מורכבים של בסיס יחיד. למתגי PCI Express יש כיוונים מפורשים למעלה (לכיוון ה-root complex) ולמטה (לכיוון ההתקנים המחוברים). המתגים נועדו בעיקר להרחיב את קישוריות ההתקנים ההיקפיים במערכות.

במקור, PCI Express אינו תומך בקישוריות מעבדים עמית-לעמית. השימוש ב-PCI Express לסוג קישוריות שכזה עשוי להיות מורכב מאוד. כשמנסים לבנות כבל חיבור למספר מעבדים מתוך PCI, יש צורך לחרוג ממפרט ה-PCI הבסיסי וליצור מנגנונים חדשים שימפו מרחבי כתובות ומזהי התקנים בין מעבדים רבים שהנם מעבדים מארחים או מעבדי בסיס. עד היום אף אחד מהמנגנונים המוצעים לעשות זאת – מיתוג מתקדם (AS), גישור לא שקוף (NTB) או וירטואליזצית קלט/פלט (MR-IOV) רב-בסיסית – לא הצליח מבחינה מסחרית, וכן אינו תומך בטופולוגיות שרירותיות.

PCI Express אינו פרוטוקול אשר ניתן לניתוב, כמו אתרנט או RapidIO. הוא מגדיר מרחב כתובות יחיד גדול שהתקנים ממופים אליו. ביצוע פעולות טעינה או אחסון לכתובות בטווח הכתובות המקושר להתקן ספציפי הוא הדרך הנפוצה ביותר לתקשר ב-PCI Express.

התקני גשר או מתג של PCI Express חייבים לזהות את ההתקן המיועד באמצעות השוואת כתובת ה-32 סיביות או 64 סיביות שכלולה במנה כנגד מערך של ערכי בסיס וערכי מגבלה ולהעביר את המנה להתקן או למתג במורד המקושר לכתובת הכלולה במנה.

סכימת ניתוב מזהה נפרדת מהווה גם היא תמיכה כאשר התקנים מזוהים לפי מספר אפיק, מספר התקן ומספר פונקציה. סכימת ניתוב מזהה זו משמשת בדרך כלל להגדרות תצורה ולתקשורת המבוססת על הודעות. סכימה זו אינה שימושית להעברת נתונים. מספר האפיק, מספר ההתקן ומספרי הפונקציה לניתוב המזהה, כמו הקצאות מרחב הכתובות, מוקצים במהלך העלאת וזיהוי המערכת.

ניתוב של מנת PCI Express משתמש בשלושה אלגוריתמים שונים, בהתאם לסוג המנה. כל האלגוריתמים יוצאים מנקודת הנחה שלמערכת יש טופולוגיית עץ, עם root complex בראשה ומפת כתובות גלובליות שמנוהלת על ידי ה-root complex:

מבוסס כתובת: אוגרי כתובת בסיס ותחום (base and limit registers) מקשרים טווחי כתובות עם יציאות במתג PCIe. יש שלוש עד שש ערכות של אוגרי כתובת בסיס ותחום לכל יציאת מתג.

מבוסס מזהה: לכל יציאה של מתג PCIe יש טווח של מספרי אפיקים שמקושרים אליה. מנות מנותבות בהתאם למספר האפיק, מספר ההתקן ומספר הפונקציה שלהן.

משתמע: מנות של הודעות PCIe עושות שימוש בניתוב 'משתמע', שבו הניתוב נקבע לפי סוג ההודעה.

PCIe התפתח ועכשיו תומך ב"גישור לא שקוף", שמאפשר להתקני root complex נפרדים לשלוח טרנזקציות זה לזה. בדרך כלל, גישור לא שקוף דורש תרגום של כתובות מנות ומספרי אפיקים/התקנים/פונקציות כדי לפתור התנגשויות בין מפות הכתובות הגלובליות של התקני ה-root complex השונים. אין סטנדרטים ליישום יכולת תרגום זו.

מבלי לשפר את יכולות הפרוטוקול הבסיסי של PCI Express, אין דרך טבעית לתמוך בקישוריות מעבד עמית-לעמית. מוצרים שמפרסמים מיתוג מרובה מארחים של PCI Express למעשה מעבירים פונקציונליות NIC (כרטיס רשת) דמוית אתרנט אל התקן ה"מיתוג".

בעוד שעשוי להיות ערך לפעולה כזו, התוצאה היא התקן מיתוג מורכב יותר, ופתרון קנייני של ספק יחיד. גם היכולת לדרג מתגים או לתמוך בטופולוגיות כמו קישוריות רשת או fat tree היא בעייתית מאוד בגישה זו. יהיה קשה להבטיח יכולת פעולה הדדית בין מוצרים של ספקים שונים.

יש לציין שהן PCI Express והן RapidIO נועדו לשילוב הדוק במערכת המשנה של הזיכרון בהתקן SOC. הדבר מאפשר זמן אחזור מצומצם בהרבה ותקשורת רוחב פס גבוהה יותר. ממשקי מארג מחוברים חיצונית, כמו Infiniband או אתרנט, תמיד ידרשו שלב נוסף של תקשורת כדי להעביר נתונים מזיכרון של מעבד או אליו.

לסיכום, במערכות שבהן יש התקן מארח ברור יחיד, ומעבדים ומאיצים אחרים פועלים כהתקנים משניים, PCI Express הוא בחירה טובה למדי עבור קישוריות. אולם כדי לחבר מעבדים רבים ביחד במערכות מורכבות יותר, ל-PCI Express יש מגבלות משמעותיות בטופולוגיה ובתמיכה לקישוריות עמית לעמית.

טרנזקציות וטופולוגיה של אתרנט

מפתחים רבים ראו באתרנט פתרון לחיבור מעבדים במערכות. האתרנט התפתחה משמעותית ב-35 השנים האחרונות, ובדומה לעלייה במהירויות העיבוד של מחשבים, פס הרוחב שלה בשיא גדל בקביעות. כרטיסי האתרנט הזמינים כיום יכולים לתמוך ב-40 ג'יגה-סיביות לשנייה, תוך פעולה על ארבעה צמדים של SerDes עם אותות של 10 ג'יגה-סיביות לשנייה. כרטיסים כאלה מכילים משאבי עיבוד משמעותיים בפני עצמם, שיוכלו לתמוך בשידור ובקליטה של מנות במהירויות אלה.

כדי להשתמש באתרנט, שהנה חיבור אובדני של מאמץ מיטבי (best effort), ככבל חיבור יעיל למעבד, יש צורך בהאצה משמעותית של הטרנזקציות כדי להימנע מהתקורה ומזמן האחזור של התוכנה, וכן בשיפורים ב-MAC של האתרנט ובהתקני המיתוג של האתרנט עצמם, כדי לצמצם את זמן האחזור. אפילו עם שיפורים אלה, פעולות תקשורת בין מעבדים בדרך כלל משמשות רק לטרנזקציות בלוק גדולות, כדי לסלק את התקורה ואת זמן האחזור הכרוכים בשימוש באתרנט.

שני תקנים חשובים פותחו כדי לציין מנגנונים לביצוע פעולות העברה של זיכרון מרחוק (RDMA) באתרנט. פרוטוקול iWARP RDMA הוצג לראשונה בשנת 2007, וזכה להצלחה מוגבלת. פרוטוקולiWARP מסתמך על הוספת כתובות TCP ו-IP כדי לספק מנגנון העברה אמין.

רוב הפיתוח של RDMA באתרנט ממוקד עכשיו בטכנולוגיית RoCE החדשה. RoCE, שאותה מבטאים כ'רוקי', היא ראשי התיבות של RDMA over Converged Ethernet. ההעברה ל-RoCE נעשית אמינה יותר באמצעות הוספת מספר שיפורים לפרוטוקול, המוכרים באופן קולקטיבי בשם DCB (גישור מרכז נתונים). שיפורים אלה מספקים מנגנון להימנעות מהשמטת מנות, הודות לצפיפות הרשת.

חשוב לציין ש-DCB אינו מבטיח שהמנות לא יושמטו ברשת אתרנט, אלא רק מספק מנגנונים שבהם רשת יכולה להשתמש כדי לשדר נתוני צפיפות ולהימנע ממצבים שבהם מנות יוכרחו להישמט בשל הצפיפות. DCB גם אינו מבטיח שהמנות לא יאבדו בגלל שגיאות במנות או ניהול לא טוב של המאגרים.

בשל סיבות אלה, האתרנט היא טכנולוגיה כמעט ללא אובדן. רק 'כמעט' משום שמנות עדיין יכולות ללכת לאיבוד בשל שגיאות או ניהול לא טוב של מאגרים. אך מערכות שתוכננו בעזרת DCB עדיין יצטרכו לסבול מנות שאבדו או שאינן תקינות. מכיוון שפרוטוקול TCP/IP אינו משמש יחד עם פרוטוקול RoCE, הטכנולוגיה גם מוגבלת לרשת אתרנט יחידה של שכבה 2, ולא יכולה לעבור את גבולות הנתב.

הן iWARP והן RoCE מיושמים בדרך כלל באמצעות מעבדי האצה השוכנים בכרטיס הרשת עצמו, מספקים כגון Chelsio ו-Mellanox. אפילו עם תמיכת DCB, עדיין חובה לנהל בזהירות טרנזקציות RDMA כדי לצמצם את תקורת התקשורת. יעילויות של תוכן מנה באתרנט טובות למנות גדולות מאוד, ורעות מאוד למנות קטנות.

אם מודל התקשורת שלך מבוסס על הודעות קטנות, אזי אתרנט לא תהיה יעילה במיוחד. לדוגמה, עבור תוכני מנה של 100 בתים, טרנזקציות אתרנט המשתמשות ב-UDP יעילות רק ב-60% מבחינת תוכן מנה לסיביות בכבל, ויעילות זו מידרדרת משמעותית עבור תכני מנות הקטנים מ-100 בתים. טרנזקציות המשתמשות ב-TCP יהיו פחות יעילות.

בעוד שהתרשים הקודם מראה את היעילות של הסיביות על הכבל, האיור הבא מציג את זמן האחזור של טרנזקציות הודעות עבור הודעות של 100 בתים המיושמות באמצעות הפרוטוקולים RoCE ו-iWARP שפועלים באתרנט ברוחב פס של 10 ג'יגה-סיביות. נתונים אלה מראים קודם כל את השוני הגדול בזמני אחזור עבור iWARP בשל השימוש ב-TCP, עם זמן אחזור של טרנזקציה, הנע בין 10 מיקרו-שניות לבין למעלה מ-60 מיקרו-שניות.

מיתוג אתרנט

בסביבות מרכזי נתונים, האתרנט נמצאת בכל מקום. האתרנט השתמשה במקור באלגוריתם "ההתאמה האפשרית הארוכה ביותר" בעת ניתוב מנות IP. באופן זה נתמכו פרוטוקול העץ הפורש (spanning tree) של האתרנט ופונקציונליות אחרת של רשת. אולם זה היה מורכב, צריכת החשמל הייתה גבוהה, וזמן האחזור במתגים גדל באופן משמעותי.

מתגי אתרנט התפתחו והחלו לתמוך בצדדים שונים של תגי רשת מקומית וירטואלית (VLAN), שמאפשרים לנתב מנות באמצעות שיטת יצירת אינדקס פשוטה יותר. גישות לרשת מוגדרת תוכנה (SDN) כגון OpenFlow מנסות להגדיר גישות נפוצות להעברת טבלאות שבהן כל המתגים יכולים לתמוך.

כך קל יותר למרכזי נתונים ולרשתות של מפעילות סלולריות לתמוך בפונקציונליות מתוחכמת יותר, כגון חומות אש, תעדוף, ניתוב ורשתות LAN וירטואליות. טכנולוגיות כמו SDN מעלות את המורכבות של הסיליקון של מתג האתרנט, כדי לספק יכולת תכנות ויכולות גבוהות יותר לרשתות של מרכזי נתונים. בעוד שתכונות אלה שימושיות למדי לתקשורת של מחשב-למחשב במרכז נתונים, הן מוסיפות צריכת חשמל, עלויות ומורכבות בלתי הכרחיות כשמשתמשים באתרנט כפתרון נקודה-לנקודה פנימי או כפתרון מארג בתוך מחשבים משובצים.

אתרנט ופרוטוקולי ה-TCP/IP שתומכות בה נועדו לעבוד בסביבה אובדנית ודינמית. זהו ללא ספק הפתרון הנכון לחיבור מחשבים נפרדים. אולם, כאשר מחשבים הופכים לווירטואליים ומתארחים במערכים של מעבדים בעלי חיבור הדוק, תקורת פרוטוקולי התקשורת מבוססי-התוכנה של האתרנט וכבלי החיבור האובדניים הופכת לברורה.

הבעיה הגדולה ביותר קשורה לזמני אחזור של טרנזקציות. כפי שהוזכר קודם, תקשורת חד-כיוונית בקישור אתרנט ממותג באמצעות TCP/IP נמשכת בדרך כלל עשרות מיקרו-שניות. מעבד רב-ליבתי אופייני יכול לבצע מיליוני פעולות במהלך הזמן שנדרש לשליחה וקבלה של הודעת תקשורת בין מעבדים.

פרוטוקול האתרנט אינו תומך באף סוג של הודעת אישור אוטומטית למנה, כלומר – היעד של מנת אתרנט לא מאשר בחזרה לשולח באופן אוטומטי את קבלת המנה או את תוצאות הבקשה. בכך שמשאירים לתוכנה את אישור האמינות של המנה, השימוש באתרנט מוסיף זמן אחזור משמעותי לטרנזקציות ברמה נמוכה, בהשוואה לפרוטוקולים כמו PCI Express ו-RapidIO.

לדוגמה, אם היה נעשה שימוש באתרנט לביצוע משהו כמו פעולת קריאה של זיכרון מרחוק, פעולת RDMA נפוצה מאוד, המנה שמכילה את בקשת הקריאה תצטרך להתקבל על ידי חומרת כרטיס הרשת של האתרנט, והתוכנה היא זו שתפענח אותה. אז יהיה צורך לסווג את המנה, מכיוון שהיא עשויה להיות כל סוג של מנה. ברגע שזוהתה כפעולת קריאת RDMA, הבקשה תועבר לתוכנת RDMA, שתפענח את הבקשה, תזהה את הנתונים המבוקשים, ותכין את המנה/המנות של התגובה באתרנט. מנת התגובה תעביר אז את הנתונים המבוקשים בחזרה אל המבקש, באמצעות ה-TCP/IP וערימת האתרנט ותוכנת מנהל ההתקן.

כפי שמדגימים נתוני Mellanox, זמני אחזור של הודעות במקרה הכי טוב עבור אתרנט ברוחב פס של 10 ג'יגה-סיביות הם בטווח של 6 מיקרו שניות, וזמני אחזור ממוצעים קרובים יותר ל-13 מיקרו שניות כשמשתמשים בטכנולוגיית RoCE המואצת. ב-PCI Express וב-RapidIO כאחד, ניתן לנהל בקשה לקריאת נתונים בצורה מלאה בחומרה, ללא התערבות של תוכנה. זמן האחזור בטרנזקציות ב-PCI Express וב-RapidIO יהיה בדרך כלל פחות ממיקרו שנייה אחת, ונמוך עד 500 ננו-שניות. זה קרוב בהרבה לזמני האחזור שרואים כאשר מתקשרים עם משאבים על השבב, או עם DRAM.

הצעת הערך של האתרנט ידועה היטב, אך ישנן שאלות משמעותיות הקשורות לשימוש בה כאמצעי תעבורה לקישוריות מעבדים במערכות בעלות צימוד הדוק. בעוד שהאתרנט היא ללא ספק הבחירה הנכונה לחיבור שרתים ומחשבים ביחד, ככל שדרישות העבודה ברשת עולות, מונעות בעקבות דרישות לרשתות מוגדרות תוכנה (SDN), המתגים שנמכרים כמתגי אתרנט הולכים ומקבלים את היכולות לעשות יותר ויותר, ומתקרבים לנתבים מבחינת המורכבות שלהם.

מתגי ה-SDN החדשים מקבלים החלטות מיתוג המבוססות על מידע מנות עמוק בהרבה, כולל כתובת ה-IP, מספר יציאת ה-TCP, וייתכן שההחלטות אפילו מתבססות על נתוני היישום הקשור שאליו מיועדת המנה. במצטבר, השילוב של עיבוד טרנזקציות תוכנה, עיבוד כתובות MAC של אתרנט (לעתים קרובות עם האצה), ולאחר מכן זמן אחזור של מיתוג אתרנט או SDN, מוסיף מורכבות, עלות, ובאופן בלתי נמנע פיזור חשמל גבוה יותר בתוך מערכות, בעוד שניתן להשתמש בגישות חיבור הרבה יותר ממוקדות וחסכוניות בחשמל.

טרנזקציות וטופולוגיה של RapidIO

RapidIO תוכנן לשמש ככבל חיבור למארג (fabric) של המעבד. השימוש הנפוץ

ביותר ב-RapidIO הוא במערכות מוטבעות הדורשות אמינות גבוהה, זמן אחזור נמוך (בדרך כלל תת-מיקרו שניות) והפעלה דטרמיניסטית. הוא נועד לתמוך בחיבור של סוגי מעבדים שונים מיצרנים שונים, ביחד במערכת יחידה. בשל כך הוא נמצא בשימוש נפוץ בציוד תשתית אלחוטית, שבה יש צורך לשלב מעבדים למטרה כללית, מעבדי אות דיגיטלי, FPGA ומעבדי תקשורת ביחד במערכת מהודקת בעלת זמן אחזור נמוך ואמינות גבוהה.

מודל השימוש של RapidIO יצר את הצורך לתמוך בטרנזקציות זיכרון-לזיכרון, כולל פעולות קרא-שנה-כתוב אטומיות. כדי לעמוד בדרישות אלה, RapidIO מספק מבני RDMA ישיר, הודעות ואיתות שניתן ליישם ללא התערבות של תוכנה.

במערכת RapidIO, מעבד יכול להוציא טרנזקצית טעינה או אחסון, או שמנוע DMA משולב יכול להעביר נתונים בין שני מיקומי זיכרון, ופעולות אלה יבוצעו במארג RapidIO שבו כתובות המקור או היעד עבור הפעולות נמצאות במארג ה-RapidIO. פעולות אלה יקרו בדרך כלל ללא התערבות תוכנה. כמו כן, מבחינת המעבד, הן אינן שונות מטרנזקציות זיכרון רגילות.

RapidIO תוכנן גם לתמוך בטרנזקציות של עמית-לעמית. תמיד מניחים שיהיו מעבדים רבים מארחים או ראשיים במערכת ושמעבדים אלה צריכים לתקשר זה עם זה באמצעות זיכרון משותף, פסיקות והודעות. ניתן להגדיר מעבדים מרובים, עד 64 אלף, ברשת RapidIO, כל אחד עם מרחב הכתובות המלא שלו.

מנגנונים לניתוב מנות התפתחו בכיוונים שונים עבור הטכנולוגיות השונות.

RapidIO משתמש בסכימת ניתוב פשוטה וגמישה, המבוססת על מזהה התקן, שהוא ערך המשמש לזיהוי נקודת קצה ברשת RapidIO . לנקודות קצה יכול להיות יותר ממזהה התקן אחד. לכל מנה של RapidIO יש מזהה יעד, שהוא מזהה ההתקן של נקודת הקצה שצריכה לקבל את המנה, ומזהה מקור, שהוא מזהה ההתקן של נקודת הקצה שיצרה את המנה.

מתגי RapidIO משתמשים במזהה יעד למנות כאינדקס בטבלה. כל ערך בטבלה מציין את היציאה, או את וקטור הסיביות של היציאות עבור שידור לקבוצה, שאליו יש לשלוח את המנה. ברגע שמנה מגיעה ליעדה, נקודת הקצה יכולה לנסח תגובה. מידע הניתוב בתגובה נוצר באמצעות שימוש במזהה המקור של הבקשה בתור מזהה היעד של התגובה, ובמזהה היעד של הבקשה בתור מזהה מקור התגובה. למתגיRapidIO אסור לשנות מנות.

RapidIO גם מספק קו הפרדה ברור מאוד בין הפונקציונליות של מתגים ושל נקודות קצה. מתגי RapidIO מבצעים החלטות מיתוג רק בהתבסס על זוגות של כתובות מקור/יעד מפורשים ועל עדיפויות מפורשות. כך נקודות הקצה של RapidIO יכולות להוסיף סוגי טרנזקציות חדשים מבלי לדרוש שינויים או שיפורים בהתקני המתג.

ככל שיותר ויותר מהמערכת הופך להיות משולב ביחידה אחת של סיליקון, PCI Express ואפילו האתרנט משתלבות בתוך המעבדים – שנקראים עכשיו, כראוי, התקניSOC (מערכת על שבב). אולם שילוב זה לא שינה את אופי הטרנזקציות שכבלי החיבור הללו מספקים.

מפרטRapidIO 3.0 החדש, המוכר גם בשם 10xN, מגביר את מהירות הנתיב היחיד ל-10 ג'יגה-סיביות לשנייה, ותומך בעד 16 נתיבים הפועלים במקביל, במהירות של עד 160 ג'יגה-בתים לשנייה ברוחב פס חד-כיווני לקישוריות במערכות. מפרטRapidIO 3.0 נועד גם לפעול באותו טווח וטופולוגיות מחברים שנתמכים במפרט ה-2 הנוכחי, כלומר, תמיכה בסביבות סטנדרטיות של לוח אם ומחברים כגון ATCA ו-VPX.

RapidIO נתמך גם באקו-סיסטמה איתנה של ספקי מתגים, IP, מעבדים ו-FPGA, ונמצא בשימוש רחב בתשתית אלחוטית ובציוד משובץ לביצועים גבוהים, עם עשרות מיליוני יציאות שנשלחות מדי שנה.

מהי המשמעות

של כל זה?

הצעת הערך של RapidIO מוכרת היטב בשוק המוצרים המוטבעים מזה שנים רבות. עכשיו צצה ההזדמנות להעביר את הצעת הערך הזו לשווקים יותר 'מיינסטרימיים' של עיבוד נתונים, המתפתחים ודורשים רבים ממאפייני המערכות שרשתות התקשורת דורשות כבר מזמן.

עם הצגתה של הווירטואליזציה, שרתים מבוססים על ארכיטקטורת ARM והתקני SOC בשילוב גבוה, אנו רואים עכשיו את השלב הבא של התפתחות המחשוב בביצועים גבוהים. התפתחות זו היא לכיוון אשכולות מעבדים בצימוד הדוק יותר, המייצגים חוות מעבדים שנבנו לארח מאות עד אלפים מחשבים וירטואליים. אשכולות מעבדים אלה יורכבו מעד אלפי התקני SOC מרובי ליבות, המחוברים באמצעות כבלי חיבור של מעבדים בעלי ביצועים גבוהים וזמן אחזור נמוך. ככל שכבל החיבור יהיה יעיל יותר, כך הביצועים והחיסכון של המערכת ישתפרו.

טכנולוגיות כגון PCI Express ואתרנט ברוחב פס של 10 ג'יגה-סיביות לא יעברו מהעולם בקרוב, אך הן גם לא יהוו את הבסיס למערכות המחשוב העתידיות הללו, בעלות הצימוד ההדוק. PCI Express אינו מארג, ויכול לתמוך באמת בקישוריות של מספר קטן בלבד של מעבדים ו/או ציוד היקפי. הוא ישמש רק כגשר להתקן שער למארג. באתרנט ברוחב פס של 10 ג'יגה-סיביות ניתן להשתמש כמארג, אך יש לו דרישות משמעותיות לעיבוד פרוטוקול חומרה ותוכנה. גדלי המסגרות שלו, המגוונים מאוד בגודלם (46 בתים עד 9000 למסגרות ענק), יוצרים צורך בלוגיקת עיבוד מהירה מאוד שתתמוך בהרבה מנות גדולות, ובמאגרים גדולים מאוד שיתמכו במנות גדולות מאוד בנקודות קצה ובמתגים. השימוש ב-PCI Express או באתרנט ברוחב פס של 10 ג'יגה-סיביות – או שיגביל את הטופולוגיות והקישוריות הזמינות, או יוסיף עלויות ותקורה לפתרון. מגרעות אלה יוצרות הזדמנויות למארגים קנייניים, או לפתרונות פתוחים כגון RapidIO בשוק חדש ומרתק זה.

הטמעת מערכות שרתים, אחסון ורישות משולבות מהווה הזדמנות ליצרני ציוד מקורי לחדש. מרכיב עיקרי בחדשנות זו יהיה קישוריות המערכת הפנימית. RapidIO הוא טכנולוגיה בשלה ומוכחת, שיש לה המאפיינים הדרושים להצלחה בשוק זה.

כפי שקרה בתשתית האלחוטית, שבהRapidIO הפך להיות ממוצר חדשני לתקן דה פקטו של כבלי חיבור לתחנות בסיס, כך האתגר הגדול ביותר של RapidIO בתחומי השרתים, האחסון והמחשוב בביצועים גבוהים (HPC) יהיה לחצות את התהום שבין החדשנים של ימינו והשווקים המקדימים לאמץ את המצאותיהם, לבין שיווק המוני משגשג.