מבוא

כל הרעש הנוצר בימים אלה בעולם הממירים הוא בגין ה-GSPS, הידוע אחרת בשם RF-ADC. עם ממירים בעלי קצב דגימה כה גבוה הזמינים בשוק, דבר זה חושף את Nyquist עד כדי פי עשר בהשוואה לחמש שנים אחורנית. הרבה מאוד נדון על היתרונות להשתמש ב-RF-ADCs ואף לתכנן איתם וללכוד נתונים בקצבים כה גבוהים. תודה לתאגיד JESD204x. אולם שיקול אחד נראה שנשכח, אות ה-DC הצנוע.

- איור 3. אי-תאום CM בין המגבר והממיר

- איור 2. דוגמאות של יישומים צמודי AC לעומת DC עבור חזיתות מגבר/ממיר

- איור 1. דוגמה של אותות באופן הפרשי ומשותף

תכנון עיצוב המבוא, או ה"חזית", מלבד ממיר אנלוגי לדיגיטלי (analog to digital -ADC) בעל ביצועים גבוהים, הוא תמיד קריטי בהשגת ביצועי המערכת הרצויים. אופיינית, המוקד הוא בלכידת תדרי פס-רחב, מסוג RF-y, כגון גדולים מ-1 גיגה-הרץ. אולם, ביישומים אחדים אותות DC או קרובים ל-DC דרושים גם כן וניתנים להערכה על-ידי המשתמש הסופי מאחר שגם הם נושאים מידע חשוב. לכן, ייטוב תכנון החזית כדי ללכוד הן אותות DC והן אותות רחבי-פס דורש חזית צמודת-DC המובילה כל הדרך אל הממיר המהיר.

בשל טבע היישום, תכנון חזית אקטיבי ידרוש פיתוח כדי להשתמש בחזית פאסיבית או balun כדי לצרף את האותות לתוך הממיר הם צמודי AC בהכרח. במאמר זה, סקירה על חשיבות אותות האופן המשותף (common mode) וכיצד להזיז את רמת חזית המגבר תוצג בדוגמה מתוך פתרון של מערכת ממשית.

- איור 4. דוגמה של שרשרת אותות מגבר/ממיר DC ל-WB

- טבלה 1. מטריצת אופן משותף

אופן משותף: סקירה

רבות מהשאלות של התמיכה הטכנית של לקוחות עדיין באות מלקוח כאשר קיים חוסר הבנה של הפרמטר הזה או מה ששני התקנים מסוגלים לבצע. דפי הנתונים של ממירי A/D מציינים דרישת מתח באופן משותף (common mode) עבור המבואות האנלוגיים. אין מידע מפורט רב בנושא זה, אולם יש לשמור על משוב החזית הנכון במגמה להשיג ביצועי ADCs נקובים בקנה-מידה מלא.

ל-ADCs עם חוצצים משולבים יש רמה של אופן משותף בעלת משוב פנימי של מחצית ההספק בתוספת מפל דיודות (AVDD/2+0.7V). לא דרושים כל מעגלים חיצוניים כדי ליצור ממתח למעגל זה, אולם יש לשמור עליו כדי להשתמש בצורה נכונה בממיר. לגבי ממירים ללא חוצצים (לדוגמה מבוא קבל ממותג), משוב האופן המשותף הוא אופיינית מחצית ההספקה האנלוגית, או AVDD/2. דבר זה ניתן לספק חיצונית במגוון דרכים. לממירים אחדים יש פין מיוחד המאפשר למתכנן לספק משוב דרך זוג נגדים המחוברים למבואות האנלוגיים.

לחילופין, המתכנן יכול לחבר את המשוב הפנימי לפין המרכזי של שנאי, או יכול להשתמש במחלק נגדים מחוץ לספק האנלוגי (נגד מכל זרוע של המבואות האנלוגיים אל ה-AVDD וההארקה). יש לבדוק את דף הנתונים של היצרן או קבוצת התמיכה ביישום לפני שמשתמשים בפין VREF של הממיר, מאחר שייחוסים רבים אינם מצוידים לספק משוב אופן-משותף ללא חוצץ חיצוני. זהו דבר מושך, מאחר שאתה זקוק למתח CM כאן ועכשיו, אך היזהר לא לעשות כן!

אם משוב האופן המשותף איננו מסופק או מוחזק, לממיר יהיו שגיאות שבח והיסט אשר יתרמו למדידה הכוללת. הממיר יכול לקטום ("clip") מוקדם, או בכלל לא, מאחר שלא ניתן להגיע לסקלה המלאה של הממיר. משוב האופן המשותף חשוב במיוחד כאשר מחברים מגבר לפני הממיר, במיוחד אם היישום מבקש צימוד DC. בדוק את מפרטי דף הנתונים של המגבר כדי לוודא שהמגבר יכול למלא את דרישות הניד (swing) והספקת אופן משותף של הממיר. ממירים נדחו לתהליכי גיאומטריה קטנים יותר ולכן להספקות נמוכות יותר.

עם הספקה של 1.8 וולט, מתח אופן משותף של 0.9 וולט דרוש על-ידי המגבר אם צימוד ה-DC דרוש. מגברים בעלי מתחי הספקה של 3.3 עד 5 וולט עשויים לא להיות מסוגלים לקיים רמה כה נמוכה, אולם מגברים למתח נמוך חדשים יותר יכולים כן או שהמתכנן יכול להשתמש בהספקה מפוצלת ולהשתמש בפס שלילי בפיני ה-Vss, אולם, כאשר עושים זאת, יש לזכור שפינים אחרים יידרשו גם להיות מחוברים לפס השלילי. עיין בדף הנתונים ו/או בתמיכה הישירה עבור המוצר כדי לגלות זאת.

- איור 5. ביצועי FFT אופייניים ב-507 מגה-הרץ AIN@2599 MSPS

- איור 6. ביצועי הטיית תדר אופייניים AC @2500 MSPS

- איור 7. ביצועי שיטוח הפס העובר ורמת ההנע במבוא

אופן משותף: הגדרה

נתחיל בהגדרה של מתח CM. איור 1 מראה כיצד ממיר "רואה" אותות הפרשיים או של אופן משותף. מתח CM הוא פשוט הנקודה המרכזית מסביבה נעים האותות; ראה איור 1. אתה יכול גם לחשוב על כך שזוהי נקודת מרכז או קידוד אפס. במגבר, CM נקבע על המוצאים, בד"כ דרך פין VOCM או דומה. אולם הייה זהיר, לפינים אלה יש גם דרישות של תחום הזרם והמתח. מוטב לסקור את דף הנתונים של המגבר ו/או להשתמש בנקודת משוב חזקה שאיננה מעמיסה כל מעגל סמוך או נקודת ייחוס בתוך המעגל שלך.

אל תחבר פשוט את פין ייחוס המתח של ממיר (VREF), שהוא בד"כ מחצית מהסקלה המלאה של הממיר, הוא עשוי לא להיות מסוגל לספק משוב מספיק בדיוק טוב. יהיה זהיר לסרוק את מפרטי הפינים כאן בדף הנתונים של הממיר. בד"כ מחלק מתח פשוט בעל אפיצות של 1% ו/או מוביל חוצץ יספיקו כדי לקבוע את המשוב CM הזה נכון עבור מגבר.

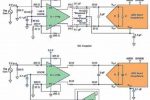

בטבלה 1, מצוינת להלן רשימה מהירה של כיצד לחבר מגבר וממיר על-פי היישום. כמו גם דוגמאות מעגלים אחדות המוצגות באיור 2.

אופן משותף: שבור

אם משוב האופן המשותף איננו מסופק או שמור, אזי לממיר יהיו שגיאות שבח והיסט אשר יפחיתו את המדידה הכוללת שבוצעה. בפשטות: מוצא הממיר ייראה כמו איור 3, או גרסה שונה כלשהי ממנו. ספקטרום המוצא ייראה כמו מבוא על-עומס בסקלה מלאה. דבר זה אומר שנקודת ה"אפס" של הממיר היא מחוץ למרכז ולא במיטבה. המתכנן עשוי למצוא שהממיר "יגזור" מוקדם או שלא יגיע לסקלה המלאה של הממיר. לאחרונה בעיה זו החמירה מאחר שהממירים משתמשים בספקים של 1.8 וולט או נמוכים יותר. פירוש הדבר הוא שמשוב ה-CM עבור המבואות האנלוגיים הוא 0.9 וולט או AVDD/2.

לא כל המגברים בעלי ספק יחיד יכולים לשאת מתח באופן משותף כה נמוך תוך שמירה על ביצועים טובים יחסית. אולם, מגברים חדשים אחדים התאימו לכך והם נמצאים בשוק כיום. לכן, יהיה זהיר לסקור באיזה מגברים ניתן להשתמש בתכנון החדש שלכם. לא רק כל מגבר ישן יעבוד מאחר שהמרווח יהפוך למאולץ מאוד והטרנזיסטורים הפנימיים יתחילו להתמוטט. אם משתמשים בספק כפול עם מגבר יש להשאיר מספיק מרווח ברוב המקרים כדי להשיג את המשוב CM הנכון. החיסרון הוא בספק נוסף, ספק שלילי שעשוי להיות בלתי-תקני, כלומר יותר פריטים ויותר הוצאות. מעגלי מהפך פשוטים יסייעו לטפל בכך.

כיצד לחבר את הכל ביחד

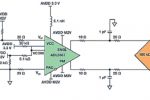

עתה שהאופן המשותף וצימוד ה-DC מובנים, אנחנו יכולים להתחיל לצרף יחד פיתרון של אותות. לדוגמה ה-ADL5567, שהוא מגבר הפרשי כפול עם שבח של 20dB. יש לו רוחב-פס של 4.8 גיגה-הרץ והוא מתאים לממשק עם ADCs GSPS, דוגמת ה-AD9625, ממיר 12 ביט 2.5GSPS בעל ממשק 8-land JESD204B. איור 4 מראה את דיאגרמת המלבנים של המערך.

בעיצוב המוצג כאן, ממשק החזית מיוטב עבור דגימת פס-רחב תוך שמירה על תוכן אות ה-DC, מאחר שהפריט הוא בעל סיבולת של +5.5 וולט. התכנון השתמש בספק מפוצל +3.3V & -2V AVDD. דבר זה מפשט את כוונון האופן המשותף בין מוצא המגבר ומבואות הממיר A/D. שניהם צריכים להיות +0.525 וולט בשני ה- AIN+ ו-AIN-. שים לב גם שזוג פונקציות הפין של המגבר אשר היו מוארקות (VSS) עם רק ספק כוח אחד מאולצות עתה אל תוך הספק של -2 וולט (VSS חדש).

מוצאי המתח CM הם ישירים למדי אך ההבנה של צורכי האופן המשותף של מבואות המגבר עשויה להיות מעט מסובכת. יש שני דברים שיש לבצע כאן למען הממשק. ראשית, מתח המבוא CM צריך להיות מעוצב עבור 0 וולט. אחרת, הזנת המגבר עם היסט תפנה את פסי המוצאים לצד אחד. דבר זה יגרום לסוגיות הביצועים המופיעות באיור 3 או גרוע מכך. בשעה שביצועי AC חלשים ייראו משרשרת האותות של המגבר והממיר. כדי לבצע זאת כל צד של מבוא המגבר צריך להרשות לזרם לעבור להארקה, או -2 וולט במקרה צמוד DC זה. לכן, נוסף נגד של 2.2 קילו-אוהם לכל מבוא של מגבר כדי "להרוג" זרם היסט זה.

הנה כיצד צא המגבר הוא ~0.525 וולט ומתח CM של המבוא הוא 0 וולט. עם נגד משוב פנימי של 500 אוהם ונגד מבוא בערך של 50 אוהם, הדבר נראה כמו 550 אוהם. או במקרה שלנו אנחנו מניחים נגד מקור של 50 אוהם במקביל עם 100 אוהם, דבר זה נותן לנו 33 אוהם. ה-20 אוהם הנוספים בטור מסתכמים לכן ב-53 אוהם. דבר זה נצמא בטור עם נגד המשוב הפנימי של 500 אוהם או סה"כ כולל של 553 אוהם. זה אומר שמפותח נגד חלוקה של 500 אוהם ו-53 אוהם. דבר זה מפתח בטורו זרם של 900 מיקרו-אמפר (או 0.525/553). כדי לצדד זאת אל ההארקה או ה-Vss החדש או -2 וולט, נוסף נגד של 2.2 קילו-אוהם או -2/2.2 קילו-אוהם= 900 מיקרו-אמפר.

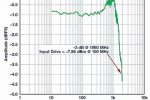

שנית, המבוא הוא מוארק, ויש לעצב אותו נכון כדי להשיג את הביצועים הטובים ביותר תוך שמירה על עיוות בסדר זוגי נמוך. שוב, ה-100 אוהם היעיל במקביל לנגד המקור של 50 אוהם יוצר שווה-ערך Thevenin של 33.33 אוהם כמצוין לעיל. זה בתורו מוחזר אופיינית אל שני הצמתים של VINכדי לאזן את המבוא של ההתקן מאחר שהוא הונהג כמוארק. אולם, במטרה לשפר את העיוות בסדר זוגי, 20 אוהם בצומת ה-VIN+ שימש כדי לשמור על עיוות נמוך למשך כל תדרי הפס ברחב. דבר זה נעשה תוך שימוש בתדר-ביניים, 500~ מגה-הרץ או ראה איור 5 כמקרה לבדיקה. דבר זה עשוי להיות מייגע מאחר שהוא תהליך איטרטיבי. לשם חישובים ומשוואות בהבנת המרת ה-SE ל-DIFF במגברים, ראה את דף הנתונים של ADA4932 או אזכור 4. מעברים של ביצועי AC אופייניים העוברים על תדרי מבוא של עד 2 גיגה-הרץ מוצגים עבור תכנון שרשרת האותות באיור 6.

הוספת סליל של 5.1nH

ראוי גם לציין את הוספת הסליל של 5.1 nH בטור עם מבוא פס ספקי הכוח החיובי. דבר זה מסייע שוב להגדיל את ביצועי הליניאריות בסדר זוגי על-גבי התדר על-ידי לכידה והנעה חוזרת של זרמים לא-מאוזנים אלה פנימית בתוך המגבר.

לבסוף, יש צורך לייטב את הממשק עבור רוחב פס חזיתי בין המגבר וה-ADC. דבר זה נעשה אופיינית גם בצורה איטרטיבית. אולם, יש מספר הערות שיש לזכור אודות מה קובע ערכים מסוימים בין שני ה-ICs. ניתן ליישם את רשימת ה"חוקים" להלן כדי להשיג את רוחב הפס הטוב ביותר מתוך הממשק.

1. ראשית, בחר נגד נחשול אחורי (kick-back) (RKB), 20 אוהם במקרה זה, מבוסס על ניסיון ו/או המלצות דף הנתונים של ה-ADC, אופיינית בין 5 אוהם ו-36 אוהם.

2. לאחר מכן, בחר את הנגד הטורי החיצוני למגבר (RA). קבע RA<10Ω אם עכבת המוצא ההפרשית היא 100 עד 200 אוהם. קבע RA בין 5 ל-36 אוהם אם עכבת המוצא של המגבר היא 12 אוהם או פחות. במקרה זה, נגד טורי של 10 אוהם נבחר עם עכבת מוצא הפרשית של 10 אוהם עבור ה-ADL5567.

3. השילוב הכולל של נגדים בטור ובמקביל הנראה על-ידי מוצאי המגבר צריך להיות קרוב לעומס המאופיין (characterized load RL) של המגבר. במקרה זה, 160 אוהם, או 2RA+2RKB+RADC=20+40+100, במעגל או באיור 4. ה-ADL5567 אופיין עם RL של 200 אוהם כך שיש לצפות לסטיות אחדות בביצועי הליניאריות אם התכנון נע הרחק מה-RL המאופיין של המגבר.

4. לבסוף, קיבול ה-ADC הפנימי, CADC, מתווסף למיצד המוצג אחרי הנגד הטורי של 10 אוהם כדי לסייע לנחשול האחורי מרשת הדגימה של ה-ADC הפנימי. דבר זה מציע גם סינון מעביר נמוכים "רך" כדי להקטין את כל ההרמוניות של פס רחב המופיעות בתוך הפס.

לשם תהליך שלם יותר בפיתוח מסננים נגד מדרוג בין המגברים וממירי ה-A/D ראה CN-0227 ו-CN-0238 או אזכורים 6 ו-7.

תוך שימוש בשיקולים לעיל פותחה תגובת שיטוח של 2 גיגה-הרץ כדי ללכוד תדרים בתוך אזורי Nyquist הראשון והשני, בהנחה של דגימה של GSPS2.5. מפרט הנע המבוא בתכנון זה מסתיים ב-8dBm- או 252mVpp בהנחה של עכבת מבוא של 500 אוהם בתדר של 100 מגה-הרץ. זוהי רמת הסקלה המלאה במבוא אותה דורש המגבר עבור הממיר כדי להשיג סקלה מלאה.

סיכום

הזנחה של מפרט מתח המבוא באופן משותף יכולה לגרום לבלבול בכל תכנון צמוד DC. אם משתמשים בדרגות מרובות, יש לשמור על רמות הופן משותף שוות תוך כדי שרשרת האותות כדי למנוע ששני הרכיבים "ייאבקו" זה עם זה. אחד מהם ינצח בד"כ בין כל שלב אם לא משולב נכון, וייצור מדידות מעוותות.

בשביל יישומים צמודי ac, השתמש בקבל צימוד בין שתי הדרגות כדי למנוע אי-תאימות של האופן המשותף. דבר זה מאפשר לתכנון לייטב את המשוב של הן מוצא המגבר והן מבוא ה-ADC לדוגמה.

אחרת, יהיה צורך לערב ספקים כפולים או מעגלי הזזת הרמה בתכנון המערכת כמתואר לעיל בתכנון הצמוד DC. לקבלת עותק של ניתוח ה-DC הצמוד לעיל, שלח לי email, או תתקשר אלי ב-Analog Devices Engineering Zone.

אזכורים

1. Quite Universal Circuit Simulator

2. Nuhertz Technologies, Filter Free Filter Design Program

3. Achieve CM Convergence between Amps and ADCs, Electronic Design, July 2010.

4. ADA4932 Datasheet, ADI

5. Kick-Back at High-Speed, Unbuffered ADCs, Electronic Design, July 2011.

6. CN-0227, High Performance, 16-Bit, 250 MSPS Wideband Receiver with Antialiasing Filter

7. CN-0238, High Performance, 12-Bit, 500 MSPS Wideband Receiver with Antialiasing Filter

8. CN-0279, High IF Sampling Receiver Front End with Bandpass Filter

9. AN-827, A Resonant Approach to Interfacing Amplifiers to Switched-Capacitor ADCs

10. Bowick, Chris, RF Circuit Design, Newnes, Feb 1997