חמישה מהשווקים הוורטיקליים הגדולים ביותר למוליכים למחצה משתפים פעולה בכדי לקדם מספר מהמגמות הנרחבות ביותר בשוק. גידול בלתי פוסק במורכבות וגודל בתכנון, שגשוג של יישובי הפריפריה, גידול ביכולות המחשוב, הגדלת קיבולת תנועת הנתונים (קלט / פלט) וצורך חיוני לצמצם את צריכת האנרגיה הגדלה. ההשפעה המשולבת של מגמות אלו משפיעה באופן דרמטי על סביבת אימות התכנון ומקדמת מגמה הולכת ומתרחבת של פלטפורמות אמולציה לחומרה.

חמשת הבסיסים התורמים למגמות אלו הינם רישות של מרכזי מידע, תקשורת / 5G, נהיגה אוטונומית, אחסון ולמידת מכונה (ML) על ידי אינטליגנציה מלאכותית (AI).

תיאור קצר של ההיסטוריה של אימות בסיוע חומרה.

לפי ברית ה- ESD, קהילה טכנולוגית בתחום מוליכים למחצה, שוק האימות בעזרת חומרה (HAV) גדל בצורה מתונה מאז 1995, כאשר הוא מפגר אחרי שווקי ההדמיה לחומרת תאור שפות (HDL) בפער מעל ל- 200 מיליון דולר במהלך העשור של 2000-2010. החל משנת 2011, קפיצה של הרווחים בשוק ה- HAV הביאה לסגירת הפערים והובילה לקפיצה נוספת בהיקף השוק ב- 2014.

ב- 2018, המציאות החדשה הפכה את הפער לטובת כלי ה- HAV. ברית ה- ESD דיווחה על מחזורי שיא בשנת 2020 עבור כלי ה- HAV בסכום של 718 מיליון דולר. ראו טבלה מס. 1.

Table #1: Revenue trends for hardware-assisted verification show growth. (Image source: The ESD Alliance, a SEMI Technology Community)

הגיוני להניח כי המגמה לאימוץ אימות בעזרת חומרה מחמשת השווקים המשמעותיים תמשיך ותואץ בעתיד הנראה לעין.

מגמות ואתגרים בשווקי רישות מרכזי נתונים, תקשורת / 5G, AD, AI/ML ואחסון מדגישים כיצד אמולטורים מובילים – התורמים הגדולים ביותר לשוק ה- HAV – יכולים לספק פתרונות. מגמות ואנליזות בנושא החשמל נידונות בקצרה בפסקה האחרונה.

תחום רישות מרכזי נתונים נהנה מגידול מואץ במיוחד הנתמך ביישומים חדשים כגון רישות מוגדר תוכנה (SDN). פרוטוקולים חדשים הכוללים תקשורת 5G , רישות תלוי-זמן (TSN) ואינטרנט לכלי רכב משחקים גם תפקיד. כל אלו תרמו להגדלת יכולות היציאות, המגיעות כעת ל- 256 ומהירויות יציאה המתקרבות ל- 800 ג'יגה-ביט / שניה, פס רשת מוגדל, ורמות השהייה נמוכות יותר. התוצאה הינה גידול מתפרץ בתחום תכנון הדגמים, הגעה למספרים של מאות מיליוני אקוויוולנטיים לשערים לוגיים והקטנת אימות קדם-סיליקוני בשל הזמן המופחת הנדרש לווידוא כי יש עמידה בביצועים וברמות צריכת האנרגיה.

Data center networking adds a host of verification challenges.

(Image source: Siemens EDA)

אמולציית חומרה עבור רישות

בכדי להתמודד מול האתגרים, אמולטור חומרה פורץ דרך חייב להחזיק בשלוש תכונות מרכזיות: פלטפורמה, אפליקציות ואקו-סיסטם.

לגבי הפלטפורמה, הקיבולת שלה חייבת להגיע ל- 15 מיליארד שערים לוגיים יחד עם מדרגיות המתחילה במיליארד שערים, תוך שמירה על מהירות ביצוע עקבית עבור כל התצורות. עליה לתמוך בזיכרונות משולשים בעלי כתובות ניתנות לגישה (TCAM) באופן טבעי, בכדי להימנע מסרבול ומידול לא יעיל. חשוב לא פחות הינו ערוץ התקשורת בין סביבת הבדיקה ובין ההתקן תחת בדיקה (DUT). הריצה באמולטור צריכה להתאפיין ברוחב פס רחב והשהייה נמוכה בכדי להתמודד עם המספר הגדל של היציאות.

לגבי אפליקציות, נדרשות הן אמולציה פנים-מעגלית (ICE) והן פריסה וירטואלית. הידור דטרמיניסטי הינו הכרח עבור מערכות ICE ומערך רחב של מתאמי מהירות הינו חיוני. עבור מצב וירטואלי, ספרייה מורחבת של פתרונות וירטואליים מוכחים (כגון VirtuaLAB Ethernet ו- VirtuaLAB PCle של חברת "סימנס") הינה חובה.

תקשורת ו- 5G

שני מאפיינים בולטים בשוק התקשורת ובמיוחד עבור אפליקציות 5G. ראשית, זרם של כ- 50,000 פטנטים בתחום ה- 5G ב- 2018 מאפיין את האצת פריסת הטכנולוגיה. שנית נדרש תוכן ייחודי של מוליכים למחצה בכדי לעמוד בדרישות לצריכת הספק נמוכה, ביצועים, גודל והשהייה במגוון רחב של אפליקציות כגון מכשירים חכמים, מוצרי קצה של IoT, מציאות מדומה ורכבים לנהיגה אוטונומית.

אמולציית חומרה עבור 5G

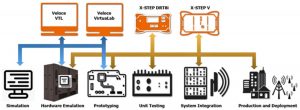

בכדי לענות על בעיות בתחום אימות התכנון ב- 5G, נדרש סט כלים כולל מקצה-לקצה המשולב בתהליך המתחיל ברמת הקניין הרוחני הקדם-סיליקוני וממשיך כל הדרך לבדיקות המעבדה לאחר שלב הסיליקון.

במחזור אימות / תיקוף מלא, התהליך כולל הדמיה, אמולציה, טיפוסי-אב, בדיקת יחידות, שילוב מערכות ובדיקות פוסט סיליקוניות. ההדמיה מכוונת לרמת אימות של IP / בלוק. אמולציית חומרה מקבלת פיקוד משלב הסימולציה בכדי לבצע אימות תתי-מערכות ובשילוב עם אפיון טיפוסי אב ב- FPGA, מאמתת ומתקפת את המערכת המלאה כולל בדיקות דרך התוכנה. פלטפורמה משולבת היטב של אמולציה ואבי-טיפוס יכולה לחלוק את אותו גורם ממריץ ואימות מקצה לקצה.

נהיגה אוטונומית

תכנון נהיגה אוטונומית מערב מספר גורמים קריטיים מההיבט של שיקולי בטיחות וביטחון בכדי למנוע מחויבויות לעיבודי Big Data הדורשים תקשורת מסיבית בין הרכב לבין מחשוב בענן.

אתגרי אימות נעים החל מהמספר ההולך וגדל של חיישנים שעשוי להגיע למעל 50 סוגים שונים, הכמות הגדלה של תוכנה המגיעה כבר היום ל 100 מיליון שורות קוד והמורכבות של החומרה והתוכנה שיש לתקפן ביחד. הדבר דורש כמויות גדולות של מחזורי אימות בכדי להבטיח כי הנהיגה ברכב האוטונומי הינה בטוחה ובטיחותית.

Figure #2: A 5G end-to-end, pre- and post-silicon development and verification flow encompasses simulation, emulation, prototyping, unit testing, system integration, and post-silicon testing. (Image source: Siemens EDA)

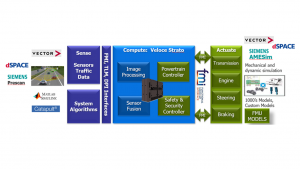

אמולציית חומרה עבור נהיגה אוטונומית

תהליך אימות / תיקוף של בקר נהיגה אוטונומית חייב להתמודד ולעסוק בחושים, חישוב והפעלה. החושים קולטים מידע מחיישנים בכדי ללכוד תרחישי נהיגה. החישוב מבצע אלגוריתמים לעיבוד תרחישים אלו ויצירת החלטה. הביצוע פועל על החלטות אלו על ידי שליחת פקודות למנוע, מערכת ההילוכים, ההיגוי ומערכת הבלימה, דבר הדורש אינטגרציה של מספר טכנולוגיות. אמולציית תוכנה מבצעת חישוב של נתוני החיישנים הנוצרים בסביבה וירטואלית כגון VECTOR, CANoe, dSPACE מתוצרת Pre scan של "סימנס" ומייצרת תגובות לשליחה ליישום פעולות דרך מודלים פונקציונאליים עבור המנוע וההגה, כגון מערכת AMESim של "סימנס" ואחרות.

AI/ML (בינה מלאכותית ולמידת מכונה)

עיצובי AI/ML מתעדים את כמות הטרנזיסטורים הגדולה ביותר המונעת על ידי ארכיטקטורה חדשה לביצוע חישובים, אחסון וגישה לזיכרון. הארכיטקטורה החדשה הינה למטרת יישומים ספציפיים כגון יחידת עיבוד טנזורים (TPU), מעבד רשת עצבית (NNP), מנוע עיבוד עצבי (NPE) כמו גם סוגי יישומים כגון אחסון 2D, 3D, שבבים, מארג FGPA ולוגיקת אינטליגנציה מלאכותית מותאמת. מנקודת המבט של האימות, קיבולת מתוכננת, מארג התיכנון, אנליזת הספק ותיקוף של עירום תוכנה הינם ארבעת היכולות שאיתם צריכה להתמודד אמולציית החומרה עבור AI / ML.

בהתבסס על מאפייני תיכנון אלו, פלטפורמת אמולציה חייבת להתמודד עם עד 15 מיליארד שערים לוגיים, לעבד תכנונים בקצב של מספר מאות מיליוני שערים לוגיים בשעה עבור זמני הסבה מהירים (TAT) בכדי למצוא ולתקן באג, הידור מחדש והרצה של אמולציה. עליה לתמוך ברוחב פס גבוה של תקשורת בין המחשב המארח והאמולטור בכדי לנהל את התנועה האינטנסיבית בין סביבת הבדיקה הווירטואלית וה- DUT. עליה לבצע אנליזת הספק מדויקת ולהוציא לפועל עירומי תוכנה של הלקוח בהתאם לאפליקציה.

Figure #3: An autonomous vehicle verification and validation environment must consider sense, compute, and actuate. (Image source: Siemens EDA)

אחסון (SSD לעומת CSD)

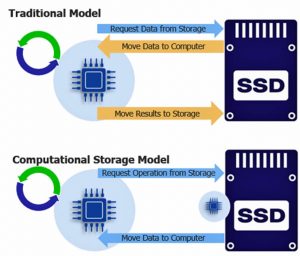

שלושה צווארי בקבוק מגבילים את כונן המצב המוצק (SSD). ראשית, מדיית האיחסון המורכבת ממארג זיכרון הבזק (Flash) NAND שהינו בעל תועלת חיים קבועה וסופית, רמת השחיקה, הצורך באיסוף נתוני זבל, הדרדרות בביצועים לאורך זמן, אמינות לא גבוהה והשהיות רנדומליות בביצועים. שנית רוחב הפס וההשהיה של ממשק המחשב המארח אינם מאפשרים ל SSD למצות את הפוטנציאל המלא שלו. שלישית, הנתונים הפיזיים של ביצועים נמוכים יותר של תנועת נתונים וצריכת חשמל. חלק מצווארי בקבוק אלו חוסלו בהתקן האיחסון המיחשובי (CSD).

ב- SSD, המחשב המארח מפיק בקשה לנתונים לדיסק האחסון. מדיית האחסון שולחת את הנתונים למחשב והמחשב כותב את הנתונים המעובדים חזרה לאחסון. ב- CSD, המחשב המקומי, במקום לשלוח את הנתונים חזרה למחשב המארח מעבד את הנתונים "במקום" ושולח את התוצאות חזרה למארח.

באופן בסיסי, מתכניי CSD יכולים לפרק ולהעביר את יכולות החישוב מהמחשב המארח למקום עצמו בכדי לשפר את הביצועים, להוריד צריכת חשמל ולשחרר את רצועת הפס PCle לשימוש של שאר המערכת.

מספר אפליקציות מרוויחות מהשימוש ב- CSD, כולל מרכזי נתונים בהיקפים גדולים מאד, זיהוי תמונות, חישובי קצה, AI/ML, בדיקות אנליטיות בזמן אמת, שאילתות לבסיסי נתונים ואחרות.

אמולציית חומרה לאחסון

גישות האימות המסורתיות ל SSD ו- CSD נחלו כישלון בשל האופי הלא- דטרמיניסטי של האחסון. אימות וירטואלי מבוסס חומרה מציע שיטות אימות חדשות. דרך וירטואליזציה ואימות מערכת מלא כולל תיקוף מלא של הקושחה, יכולים להתבצע במהירות גבוהה בכדי לקצר את זמן הביצוע עד ליציאה לשוק וליצור תגליות ארכיטקטוניות בכדי לייצר פתרונות אופטימאליים למשימות ספציפיות. וירטואליזציה של SSD מאפשרת ביצועים קדם-סיליקוניים ובדיקת השהיות בשימוש ב 5% מכמות הסיליקון בפועל.

Figure #4: Implementing a computational storage device can eliminate some bottlenecks to improve performance, lower power, and free up PCIe bandwidth.

(Image source: Siemens EDA)

מגמות ואנליזות בצריכת חשמל

תיכנון סיליקון עם צמתים תהליכיים מתחת ל 28 ננומטר מגדילה את החסרונות של צריכת חשמל דינמית במספר פלחי שוק כולל שוק הניידים וה- CPU/CGU, מרכזי נתונים, תחבורה ו- AI/ML.

זיהוי מדויק של פיקים, עמקים ונקודות חמות בתכנות הקדם-סיליקוני הינם אתגר עבור אנליזת צריכת חשמל מהירה ויעילה. לכך יש להוסיף זמני הסבה ארוכים, צריכה גבוהה של שטחי דיסק ופורמטים מגושמים ליצירת תצורות גל כגון בסיס נתונים על בסיס אותות מהירים (FSDB) ומצבורי שינוי ערך (VCD). תוצאות מדויקות וראליות יכולות להיות מושגות רק על ידי הרצת מערכות הפעלה בעולם האמיתי בקנה מידה תעשייתי כגון 3DMark, GFXBench, Geekbench, AnTuTu המחייבות מנוע בעל ביצועים גבוהים ויכולות לשלב זרימה של ולידציה.

Figure #5: Exhaustive CSD verification with emulation. (Image source: Siemens EDA)

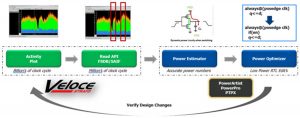

אמולציית חומרה עבור אנליזות צריכת חשמל

אמולטור חומרה מודרני יכול לייצר עקומת פעולה בשלב מוקדם של מחזור אימות התכנון על ידי הרצת אפליקציות אמת לפני רישום זמינות קוד רמת ההעברה (RTL) בכדי לאתר במהירות מתי והיכן הנקודות החמות ונקודות השפל מתרחשות. הוא יכול לקבוע מה גורם לקפיצות בתוך היררכיית החומרה ולייצר מפת נקודות חמות המראה איזה IP או בלוק הינם צרכני חשמל גדולים.

ברגע שפלטפורמת אמולצית החומרה מזהה חלון זמן בהיררכיית התכנון, היא יכולה ליצור מידע מפורט לגבי מיתוג בתוך חלונות אלו בכי להזין נתונים לכלי ניתוח צריכת החשמל. הדבר מבוצע בדרך כלל על ידי יצירת קובץ זרימה של בסיס נתונים (FSDB) או בקבצים בפורמט מחלפים לפעילות מיתוג (SAIF). גישה טובה יותר תהיה דרך גישה ישירה ל API מהאמולטור להתקן החשמל ועקיפת יצירת הקובץ להליך מהיר ויעיל יותר.

כאשר יש להתקן אספקת המתח את המידע הדרוש, הוא יכול לייצר מספרי מתח מדויקים בכדי לסייע לביצוע שינויים בתכנון ה- RTL בכדי להוריד את צריכת החשמל. לאחר ביצוע השינויים הנדרשים, מחזור אימות חדש יתקף את השינויים שבוצעו.

Figure #6: Complete power solution. (Image source: Siemens EDA)

סיכום

מגמות שוק ברישות מרכזי נתונים, תקשורת ו- 5G, נהיגה אוטונומית, אינטליגנציה מלאכותית ולמידת מכונה ואחסון משפיעות לטובה על סביבת האימות באמצעות חומרה. אימות בעזרת חומרה הינו השקעה מחייבת יחד עם הגדילה והגדלת המורכבות ומספר הממשקים של השבבים. אינטגרציה של קודי חומרה ותוכנה הופכים לקריטיים כבר בשלב התכנון המוקדם. אף כלי אימות אחר אינן יכול לעמוד באתגרים אלו.

על הכותבים

Jean-Marie Brunet הינו מנהל בכיר לניהול והנדסת מוצרים עבור אמולציה ויצירת אבי טיפוס בסימנס EDA. הוא עבד יותר מ- 20 שנה בהנדסת יישומים ובתפקידי שיווק והנהלה בתעשיית ה- EDA והחזיק משרות בתחום תכנון IC וניהול תכנון בין השאר בחברות STMicrolectronics , Cadence ו- Micron.

Lauro Rizzati הינו יועץ אימות ומומחה תעשייה בתחום אמולציית חומרה. בעבר, כיהן במשרות של ניהול, שיווק מוצרים, שיווק טכני והנדסה.