מאת: גרג ג’ו ובראד פרידן Agilent Technologies

מאת: גרג ג’ו ובראד פרידן Agilent Technologies

אתגרי בדיקות אותות מעורבים של SDR

נעשה שימוש ב- (Software Defined Radios) בצירוף של FPGAs, DSPs ותכנון אנלוגי / RF על מנת להשיג את ביצועי מערכת הרדיו. “האותות המעורבים” (Mixed signals) של תכנוני ה- SDR עשוייים, בשל טבעם, של תכנוני ה-SDR להציג מורכבויות בדיקה של אינטגרציית מערכת כאשר חומרת ה-baseband וה-RF משולבות ונבדקות יחדיו. מורכבות הבדיקה נובעת מכך מכיוון שביצועי המערכת הכוללים של ה-SDR עשויים להיות מושפעים מפגמים מצטברים בתכנון האנאלוגי, baseband

ו- RF – דבר היכול להקשות על בידוד בעיות בשלב בדיקות האינטגרציה של המערכת.

כדוגמה ניתן לבחון יישום מסנן

FPGA Finite Impulse Response המשפיע על איכות צורת הגל ותורם לביצועי ה- (Error Vector Magnitude) הנמדדים. בנוסף, ה-D/A עשוי להציג אי-ליניאריות ושעון ה-D/A עשוי להציג jitter אשר יכול להשפיע על ביצועי ה-EVM של ה-SDR. רעש פאזה LO, מסנני IF/RF, ו- gain לא ליניארי/עיוות פאזה מה- IF/RF up converter ומגבר ההספק (PA) יכולים אף הם לגרום עיוות של צורת הגל לביצועי ה- EVM של ה-SDR. לכן ביצועי ה-EVM הכוללים הינם צבירה של כל אחת מתרומות השגיאה לאורך שרשרת משדר האותות המעורבים.

טכנולוגיות (Orthogonal Frequency Division Multiple Access) של SDR יכולות גם להשתמש בטכנולוגיות (Multiple-Input Multiple-Output) על מנת להגדיל קצבי נתונים בהשוואה לגישות (Single-Input Single-Output). אלגוריתמי MIMO spatial multiplexing, שרשרות multiple transmit/receive IF/RF, ואנטנות מרובות זנים יחד עם פגמים כגון שגיאות תזמון ו- cross-coupling בין הערוצים המרובים יכולים גם הם לתרום למורכבות הבדיקה והניפוי של mixed-signal.

בעיות אלו מדגישות את הצורך בטכנולוגיה משופרת לביצוע probing בשלבים שונים לאורך שרשרת mixed-signal. זה מאפשר למהנדסי מערכת לזכות בתובנות על הפגמים התוספתיים (incremental) המתווספים לצורת הגל בכל שלב של תכנון SDR של mixed-signal. יתר על כן, probing בשלבים שונים של יישום FPGA וניפוי באמצעות אותה תוכנת מדידה של (Vector Signal Analyzer) המשמשת למדידת שלבי ה-IQ, ה-IF וה-RF האנלוגיים יכולים לספק רמה נוספת של תובנה אודות סוגיות המתרחשות ביישום ה-FPGA עצמו. מאמר זה יציג מספר דוגמאות של חקר מקרה אשר מדגישות מתודולוגיית בדיקות משופרת עבור SDRs של אותות מעורבים.

מתודולוגיה משופרת של בדיקות אותות מעורבים של SDR

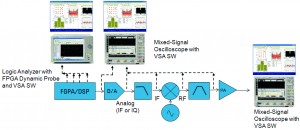

מתודולוגיית בדיקות משופרת עבור SDRs של אותות מעורבים מוצגת כדי לאפשר למהנדס מערכת ה-SDR לבצע probing בשלבים שונים לאורך שרשרת mixed-signal כמוצג בתרשים 1. מתודולוגיה זו מאפשרת למהנדס לצפות בפגמים תוספתיים (incremental) המתרחשים לאורך שרשרת אותות מעורבים, ואף יכולה לשמש לניפוי סוגיות בשלב הבדיקות של אינטגרציית המערכת. תוכנת VSA משמשת גם ב- Logic Analyzer וגם באוסילוסקופ אותות מעורבים (MSO) לביצוע ניתוח של עיוות צורת הגל וה-EVM בשלבים שונים לאורך שרשרת האותות המעורבים של ה-SDR.

Probe דינמי של FPGA יכול לשמש עם Logic Analyzer לבחירת נקודות ביניים של probe דיגיטלי signal banks ביישום FPGA. ניתן לבצע דה-מודולציה של נקודות ה- probe עם תוכנת ה-VSA כדי לקבוע את ההשפעות של יישום ה-FPGA על ה-Error Budget ה-EVM של ה-SDR (למשל מדידת ביצועי ה-EVM של מסנן FIR Root Raised Cosine). כאשר מבצעים probing לאורך שרשרת קידוד של השכבה הפיסית של MIMO, ניתן אף להשתמש ביכולת ה- probe הדינמי לצורך השוואת וקטורי הבדיקה שנמדדו אל הוקטורים המצופים כדי לאתר בעיות כגון bit reversals.

ברגע שצורת הגל של ה-SDR הומרה לאנלוגית באמצעות ממיר(י) D/A, ניתן למדוד אותה בשלבים שונים כגון IQ, IF או RF אנלוגי באמצעות אוסילוסקופ אותות מעורבים (MSO) עם תוכנת ה-VSA. זה מאפשר למהנדס לקבוע איך פגמים אנלוגיים שונים כגון רעש פאזה LO, מסנני IF/RF ו- gain לא ליניארי/ עיוות פאזה מה- IF/RF up converter ו- Power Amplifier משפיעים על ביצועי ה-EVM של ה-SDR (הערה: לא ניתן להשתמש ב- digital inputs ב-MSO עם תוכנת ה-VSA ובמקום זאת יש להשתמש ב- Logic Analyzer).

תוכנת ה-VSA מספקת המשכיות מדידה בין התחום הדיגיטלי באמצעות השימוש ב- Logic Analyzer ובין תחום ה-IQ, IF, RF באמצעות השימוש באוסילוסקופ אותות מעורבים, עובדה המאפשרת למהנדס לבצע איבחון של בעיות ולזכות בתובנות על פגמים בצורות גל בתחום הדיגיטלי והתחום האנלוגי/RF כאחד. צורות גל (Commercial-Off-The-Shelf) רבות נתמכות על ידי תוכנת 89600 VSA מתוצרת Agilent, כולל צורות גל OFDM ו- OFDMA כגון 802.11, 802.16 ו-LTE. ניתן לבצע דה-מודולציית MIMO של שני ערוצים וארבעה ערוצים באמצעות אוסילוסקופ עבור צורות גל OFDMA כגון LTE.

נבחן עתה מספר דוגמאות של חקר מקרה, כולל חקר מקרה של 802.16 באמצעות Logic Analyzer ו-probe דינמי של FPGA עם תוכנת ה-VSA, וכן חקר מקרה של LTE MIMO באמצעות אוסילוסקופ אותות מעורבים עם תוכנת ה-VSA.

חקר מקרה 802.16 באמצעות Probe דינמי של FPGA עם תוכנת ה- VSA ואוסילוסקופ אותות מעורבים

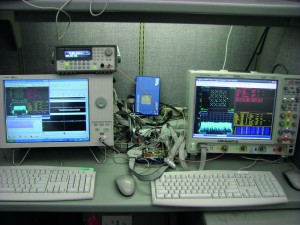

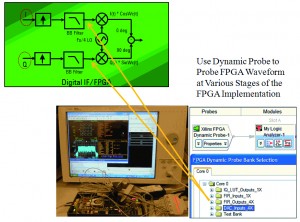

תצורת הבדיקה המוצגת בתרשים 2 משמשת לביצוע probing בשלבים שונים לאורך יישום FPGA של 802.16 באמצעות Logic Analyzer עם probe דינמי של FPGA (משמאל). ה- probe הדינמי של FPGA משמש לבחירת signal banks פנימיים שונים של ה-FPGA, אשר עוברים דה-מודולציה על ידי תוכנת ה-VSA ב- Logic Analyzer (משמאל) על מנת לבצע הערכה של תכנון ה-FPGA בנקודות probing שונות של היישום. לוח פיתוח ה-FPGA הנבדק אף כולל ממיר D/A להמרת ה-IF הדיגיטלי ל-IF אנלוגי אשר עובר לאחר מכן דה-מודולציה על די אוסילוסקופ האותות המעורבים (מימין) ותוכנת ה-VSA אשר באוסילוסקופ.

Xilinx Chipscope Pro משמש לקביעת התצורה של ליבת mux ניפוי הנקראת (ATC2 (Agilent Trace Core דור 2. הליבה מאפשרת למשתמש לגשת במהירות ל- incremental של אותות פנימיים בלחיצת כפתור של העכבר. עבור דוגמה זו קבענו את תצורת הליבה עם 3 banks של אותות שנבחרו מראש.

1) קלטי FIR ב- oversampling של 1X

2) פלטי FIR עם oversampling של 4X

3) Multiplexed digital Fs/4 IF output (DAC inputs) with 4X oversampling

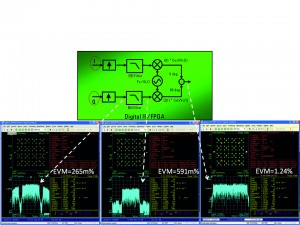

כל אחד מה- banks של ה- probe נבחר ולאחר מכן עובר דה-מודולציה באמצעות תוכנת ה-VSA שב- Logic Analyzer. תרשים 4 מציג את תוצאות הדה-מודולציה ב-1) קלטי FIR ב- oversampling של 1X (משמאל), 2) פלטי FIR עם oversampling של 4X (במרכז), ו-3) Multiplexed digital Fs/4 IF output (DAC inputs) with 4X oversampling (מימין).

ה-VSA ומדידות הספקטרום בתרשים 4 מציגים את הביצועים בשלבים שונים לאורך יישום ה-FPGA. הספקטרום במסך ה-VSA השמאלי מציג את ה-aliasing בצורת הגל הלא-מסוננת עם

1sample/symbol. ה-EVM הינו 0.265%. הספקטרום במסך ה-VSA האמצעי מציג את צורת הגל שעברה up-sampling של 4X וסינון FIR. ה-EVM הינו ברמה פחות טובה של 0.591% עקב tap coefficients FIR המיושם ב-FPGA. הספקטרום במסך ה-VSA הימני מציג את ספקטרום ה-IF הדיגיטלי הממורכז ב- 11.2, שהינו Fs/4 עבור שעון ה- 44.8 המשמש את ממיר ה-D/A. ה-EVM הינו שוב ברמה תוספתית פחות טובה (יחסית לפלטי ה-FIR) של 1.24% עקב העיוות שנוצר בעקבות ריבוב הנקודה הקבועה של Fs/4 המשמש ליצירת ה-IF הדיגיטלי שעבר מודולציה. יישום ספציפי זה אינו חושף סוגיות משמעותיות כלשהן, אולם יחד עם זאת המתודולוגיה הזו הייתה מספקת תובנות על סוגיות אם הן היו מתרחשות (למשל מקדם חיבור לא נכון באחד מה-FIRs…).

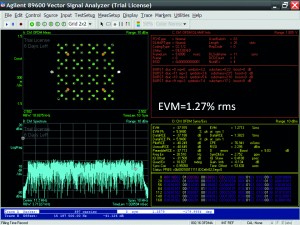

הדה-מודולציה המסתיימת בפלטי ממיר ה-D/A ונמדדת באמצעות אוסילוסקופ האותות המעורבים מוצגת בתרשים 5.

פלט ה-EVM של ממיר ה-D/A (אשר נמדד באמצעות האוסילוסקופ) הינו 1.27%, ואינו שונה משמעותית מה-EVM אשר נמדד בקלטים הדיגיטליים של ממיר ה-D/A באמצעות ה- Logic Analyzer. לפיכך ממיר ה-D/A אינו תורם עיוות משמעותי של צורת הגל בדוגמה הזו. בכל אופן, זה מציג גישה למדידת עיוות ה-EVM של צורות גל אשר תרם לה ממיר ה-D/A של SDR.

חקר מקרה LTE באמצעות אוסילוסקופ אותות מעורבים ודה-מודולציה של MIMO

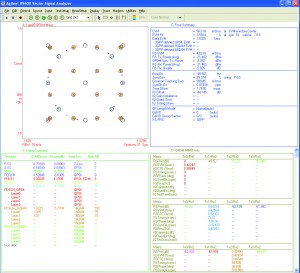

לוח ה-FPGA המשמש בחקר המקרה של 802.16 עובר קביעה מחדש של תצורתו עם קובץ .bit עבור LTE MIMO דו-ערוצי. לוח הפיתוח כולל שני ממירי D/A המאפשרים לו לשמש MIMO של שני ערוצים. אוסילוסקופים רב-ערוציים עם תוכנת ה-VSA מותאמים היטב ליישומי MIMO של שניים או ארבעה ערוצים עקב הקלטים הרב-ערוציים שלהם בעלי coherent inputs. דה-מודולציה של MIMO דורשת תזמון מותאם היטב בין ערוצי האנטנה לשמירת ה- orthogonality של אותות הייחוס (הפיילוטים, pilots).

תוצאות הדה-מודולציה של ה-VSA מוצגות בתרשים 7. הקונסטלציה מוצגת בחלק הימני העליון ומראה את מערך 16 QAM עבור ה- (Physical Downlink Shared Channel) כמו גם ערוצי סנכרון ובקרה. הערוצים השונים הנמדדים, פורמטי המודולציה שלהם ו-EVMs אינדיבידואליים מוצגים בטבלת ה- Frame Summary בחלק השמאלי התחתון של תרשים 7.

סיכום השגיאות בחלק הימני העליון של תרשים 7 מציג את ה-EVM המרוכב של בערך 0.96% אשר נמדד בלוח הפיתוח של ה-FPGA עם ממירי D/A.

טבלת מידע ה-MIMO בחלק הימני התחתון מציגה מידע אודות The orthogonal Reference Signals (pilots), antenna cross-talk, and timing error.

אותה תצורת בדיקה עם אוסילוסקופ אותות מעורבים ותוכנת VSA יכולה אף לשמש לביצוע מדידות MIMO במשדרי RF רב-ערוציים, היכן ש- crosstalk ו- cross-coupling בין ערוצי אנטנה עשויים להיות קריטיים. בנוסף, פגמי RF אחרים כגון רעש פאזה LO, ו- power amplifier gain compression ו- phase distortion בשלבים שונים בשרשרת ה-up-conversion של ה-IF/RF יכולה להיות מוערכת באמצעות תצורת הבדיקות הזו.

סיכום

SDRs של אותות מעורבים מציגים אתגרי בדיקות של אינטגרציה ברמת המערכת עבור מהנדס המערכת. פגמים בצורות גל יכולים להיות הצטברות של פגמי אותות מעורבים המתרחשים ביישום ה-FPGA, ממיר ה-D/A, ה- up-converter של IF/RF ומגבר הספק. MIMO יכול להוסיף למורכבות הבדיקה והניפוי עם שרשרות שידור IF/RF ואנטנות מרובות. שימוש בתוכנת VSA ב- Logic Analyzer וגם באוסילוסקופ האותות המעורבים מאפשר למהנדס לבצע probing לאורך שרשרת ה-SDR של האותות המעורבים על מנת לבודד סוגיות ובעיות ולקבל תובנות אודות מיקום התרחשותם של פגמים בצורות גל. יכולת ה- probing הדינמי של ה-FPGA של Logic Analyzer מוסיפה רמה נוספת של יכולת ניפוי על ידי מתן אפשרות למהנדסי SDR FPGA לבחור signal banks בתוך FPGA על מנת להעריך את התכנון באמצעות תוכנת ה-VSA בנקודות probing שונות ביישום. ההמשכיות המסופקת עם תוכנת ה-VSA ב- Logic Analyze וגם באוסילוסקופ מספקת למהנדס המערכת כלי ניתוח רב-תחומי (cross-domain) לקבלת תובנות על ביצועי SDR אותות מעורבים – בין אם זה פס בסיס דיגיטלי, IF/RF אנלוגי, או שניהם.