ביל קפיג ופראבין ונוגופאל, Xilinx

ביל קפיג ופראבין ונוגופאל, Xilinx

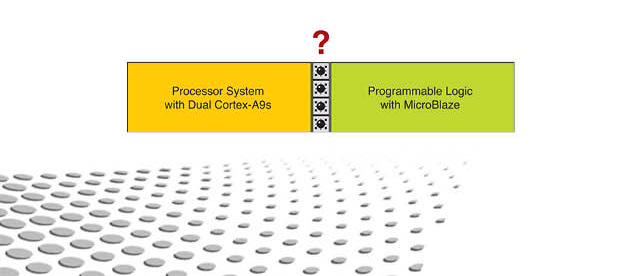

המערכת על-גבי שבב המתכנתת של זיילינקס – Zynq™-7000 כבר מתהדרת בשפע של עוצמת עיבוד מובנות. בכל זאת, נוכחותם של שני מעבדי Cortex™-A9 עוצמתיים ושל ההתקנים ההיקפיים הקשורים אליהם ביחידת עיבוד היישומים (APU) של Zynq אינה צריכה למנוע מכם להוסיף מעבד ™MicroBlaze אחד או שניים לאותה חבילה אם אתם יודעים שהיישום שלכם יצא נשכר מהתוספת.

מדוע תרצו להוסיף MicroBlaze לפתרון שממילא ניחן בעצמת עיבוד נכבדה?

ראשית, ישנה סוגיית אמינות: מבנה של "חוט" או תהליכון יחיד (single-threading) משפר באורח דרמטי את האמינות. ניתן למקם בצורה נקייה תהליכון אחד לכל מעבד Cortex-A9 (עבור משימות עתירות מחשוב), וליזום יצירה של כמה מעבדי MicroBlaze שנחוצים לנו עבור תהליכונים אחרים. שנית, ניתן להעביר כל מטלת "משק בית" שאיננה מצריכה עוצמה של Cortex-A9 ולהוציאה החוצה אל ה-MicroBlaze, מה שמספק חיסכון במחזורי הביצועים הקריטיים ושמירתם למשימות שבהן הם נחוצים באמת.

משהחלטתם לכלול מעבד MicroBlaze בתכנון מבוסס ה-Zynq שלכם, כמה סוגיות צפויות לצוץ ולהתעורר. ראשית ומעל לכל עולה השאלה כיצד תתקשר ה-APU עם ה-MicroBlaze ואילו משאבים של מערכת עיבוד (PS) יעמדו לרשות ה-MicroBlaze. לוחות רבים, ביניהם ה-ZC702 ו-Zedboard, ממפים חלק ניכר מההתקנים ההיקפיים ישירות אל הפינים המחוברים ל-PS. הפינים הללו אינם נגישים באופן ישיר ל-MicroBlaze בלוגיקה המתכנתת (PL). בנוסף, ה-PS מכילה גם מגוון טיימרים ומקורות פסיקה. האם קיימת דרך לגשת אליהם מתחום (דומיין) ה-MicroBlaze?

ממשקים בין ה-PS ל-PL

מערכת המעבד (PS) והלוגיקה המתכנתת (PL) מצומדות היטב יחדיו. כפועל יוצא, קיימים כמה וכמה חיבורים משולבים באורח הדוק בין ה-CORTEX™-A9, יחידת הבקרה SCU, ההתקנים ההיקפיים של ה-PS, ופונקציות ניהול שעון ואחרות, לבין הלוגיקה המתכנתת. למעשה, ישנם שישה סוגים שונים של חיבורים פנימיים בין ה-PS ל-PL בהם ניתן להשתמש בשילובים שונים. בנוסף, רבים מהנתיבים הללו הם סימטריים, כלומר, ה-PS יכולה ליזום או "לשלוט" בחיבורים ל-PL וה-PL יכולה לשלוט בחיבורים ל-PS.

מרבית המידע העומד לרשותנו היום מבית זיילינקס, מהערות יישום במדריכים למשתמש וממפרטים טכניים, מדגימים לנו כיצד ה-Zynq-7000 APU, המשמשת כ"מרכז התכנון", יכולה להשתמש בלוגיקה המתכנתת כדי לגשת לזיכרון, להתקנים היקפיים מבוססי PL ולהתקנים היקפיים בחומרת סיליקון כדוגמת מקמ"שי מולטי-גיגהביט, DSP48s, Block RAMs ו-PCIe block. בבואנו לבדוק כיצד ניתן להפוך את ה-MicroBlaze ל"קפטיין" של הדומיין

שלו, המקום ההגיוני להתחיל בו יהיה לבחון את ששת סוגי הממשקים, ולהתחיל עם שלושת הסוגים של ממשקי AXI: לכל מטרה, לרמת ביצועים גבוהה

וה-Accelerator Coherency port.

ה-PS מצוידת בשני ערוצי AXI מסוג "מאסטר" (שולט) אל ה-PL ושני ערוצי "סלייב" (נשלט) שנשלטים על-ידי ה-PL. "מאסטר" בהקשר הזה משמעו שערוץ ה-AXI הוא היוזם ויכול להתחיל העברות נתונים, בעוד שה"סלייב" יכול רק להגיב לנתונים שמגיעים אליו. ערוצי ה-AXI ה"מאסטרים" משמשים בדרך כלל לתקשורת עם התקנים היקפיים הממוקמים ב-PL. ערוצי ה-AXI המשמשים כ"סלייב" מגיבים לבקשות המתקבלות מה-PL, שיכולות לכלול טרנזאקציות (העברות) נתונים שמתבצעות על-ידי מעבדי MicroBlaze. ערוצי AXI אלה מתקשרים אל החיבורים הפנימיים המרכזיים של ה-PS וניתן לנתבם למשאבים רבים ושונים.

בנוסף, ישנם ארבעה ערוצים של נקודות חיבור AXI ברמת ביצועים גבוהה (רוחב 64 ביט). כל ארבעת הערוצים הללו הם "סלייבס" מנקודת המבט של ה-PS והם מחוברים לתת-מערכות ממשקי הזיכרון בתוך ה-PS. המטרה של ארבעת הערוצים הללו היא לאפשר למאסטרים ב-PL ליזום טרנזאקציות של זיכרון DDR (קצב נתונים כפול).

חיבור פנימי זה של הזיכרון ובקר זיכרון DDR הם ה"שערים" אל זיכרון ה-DDR מכל המקורות. בעוד שלמעבדי ה-Cortex-A9 יש בדרך כלל קדימות על פני חיבורי AXI מסוג סלייב, לכל אחד מארבעת חיבורי ה-AXI "סלייב" יש אות שמשמעו "טפל בי עכשיו" המעניק קדימות לערוץ שממנו מגיעה הבקשה. כאשר אות זה אינו מוצג, הארכיטקטורה משתמשת בסכמת round-robin כדי לקבוע מי מכל מגישי הבקשות יוכל לזכות בגישה לסוג הספציפי של הזיכרון.

ה- (Accelerator Coherency Port) הוא חיבור AXI PS נוסף מסוג סלייב הפועל ב-32 ביט מה-PL. מה שהופך את ה-ACP לייחודי היא העובדה שהוא מקושר ישירות אל תוך יחידת הבקרה SCU. המשימה של ה-SCU היא להבטיח לכידות בין זכרונות ה-DDR, L1 ו-L2. בעזרת ה-ACP תוכלו לגשת לזיכרון המטמון המהיר עבור כל אחד ממעבדי ה-Cortex-A9 שב-PS מבלי להטריד את עצמכם בכל מה שנוגע לסנכרון הנתונים עם הזיכרון המרכזי (כיוון שהחומרה תטפל בכל זה באופן אוטומטי). יכולת זו מקטינה באופן משמעותי את עול התכנון ומספקת דרך מהירה בהרבה להעביר נתונים בין המעבדים לבין ה-PL.

התקנים היקפיים, בלוקי נתונים וסינכרוניזציה

המפתח לגישה לבלוק ה-IOP של המערכת המתכנתת הוא החיבור לכניסת

ה-S_AXI_GP0 של ה-PS. ה-"S" מציין שמדובר בכניסת סלייב – כזו שיכולה לקבל טרנזאקציות שהיוזמה שלהן נובעת מאלמנטים ב-PL. כאשר יוצרים את החיבור בין ה-MICROBLAZE לבין כניסת ה-S_AXI_GP0, בלוק ה-IOP נפרס על פני הטווח כתובות של 0XE000_0000 עד 0XE02F_FFFF. פירוש הדבר שאף התקן היקפי אחר במרחב הכתובות של ה-MICROBLAZE אינו יכול להיות שם באופן חופף שכן חפיפה משמעה שטווח הכתובות ישמש את המעבדים בו-זמנית.

בינתיים, מספר מנגנונים תומכים בהעברת בלוקים של נתונים בין ה-MICROBLAZE לבין ה-PS, כאשר DMA מה-DDR וזיכרון על השבב (OCM) הן רק שתיים מבין כל האפשרויות. אפשרות נוספת, כפי שמיושם בתכנון הדוגמה, משתמשת ב-BLOCK RAM עם שתי כניסות. ה-PS שולט בצד אחד של בקר ה-BRAM ואילו ה-MICROBLAZE שולט בצד השני. תוכנה מנהלת את החציצה ואת השימוש בשטח זיכרון ה-BRAM המשותף, שכן לשני הצדדים גישת קריאה/כתיבה מלאה אל כל תכניו של זיכרון זה.

הסוגיה האחרונה קשורה לאופן שבו מסנכרנים אירועים בין ה-MicroBlaze לבין ה-PS. ה-PS מכילה שפע של טיימרים וניתן ליזום יצירה של כמעט כל מספר שהוא של טיימרים ב-PL. התכנון המופיע בדוגמה משתמש בערוץ אחד בתוך אחד ההתקנים ההיקפיים של שלושה טיימרים/מונים כדי לחולל פולס של 100 מילישניות. ה"טריק" כאן הוא להבין שה-TTC מחולל צורת גל שניתן לגשת אליה מחוץ ל-PS, אבל פסיקת ה-TTC זמינה רק בתוך ה-PS. ניתן לעקוף את הבעיה הזו בעזרת שימוש בצורת הגל עצמה כפסיקה למעבד ה-MicroBlaze. לחלופין, ניתן להשתמש בטיימר חומרה (טיימר AXI או טיימר אחר בקידוד המשתמש) כדי לספק פסיקה הן ל-PS והן ל-MicroBlaze.