ישראל שם-טוב, Future Electronics

שנים האחרונות חזו בהתרבות של סוג חדש של מעבד רב-תכליתי המכיל חומרת מאיץ ליחידת עיבוד וידיאו (Video Processing Unit – VPU). ארכיטקטורה זאת מספקת חלופה לגישה המסורתית המבוססת על DSP אשר מיישמת עיבוד וידיאו בתוכנה. בשעה שמערכת DSP יכולה לתמוך במגוון רחב של תבניות וידיאו, הדרישה הגוברת לחישוב מהיר יותר של תזרימים של נתוני וידיאו מאמצת DSP רבים עד לקצה גבול היכולת.

לפיכך, חומרות מאיץ ליחידות עיבוד וידיאו מוצאות חן כי הן מציעות תקורה נמוכה של יחידת עיבוד מרכזית (CPU – Central Processing Unit) ותצרוכת הספק נמוכה יותר מהמערכת המבוססת על DSP.

עתה יצרני מוליכים למחצה שואפים להוסיף יתרון שלישי, מכריע: קלות בשימוש על ידי מהנדס תיכון המערכת. מאמר זה בוחן את הפעולה והבקרה של אחד מהאבזרים המובילים בשוק זה,

ה-i.MX53 מ-Freescale ומראה איך מאפיינים המובנים בחומרה הופכים את היישום של וידיאו באיכות גבוהה לפשוט יותר מאי-פעם.

ארכיטקטורת חומרת מאיץ VPU

חומרת מאיץ VPU במעבד היישום i.MX53 הנה טיפוסית לסוגה בכך שהיא מספקת תמיכה למגוון רחב של תבניות וידיאו. אלה כוללות את H.264 BP/MP/HP, VC-1 SP/MP/AP, MPEG-4 SP/ASP למעט GMC, DivX (Xvid), MPEG-1/2, Sorenson Spark ו-RV-8/9/10. ה-VPU בחומרה יכולה לפענח וידיאו (1920×1080) ולקודד וידיאו (1280×720). היא תומכת גם בפענוח מרובה ובתקשורת רב-צדדית דו-כיוונית מלאה בו-זמנית.

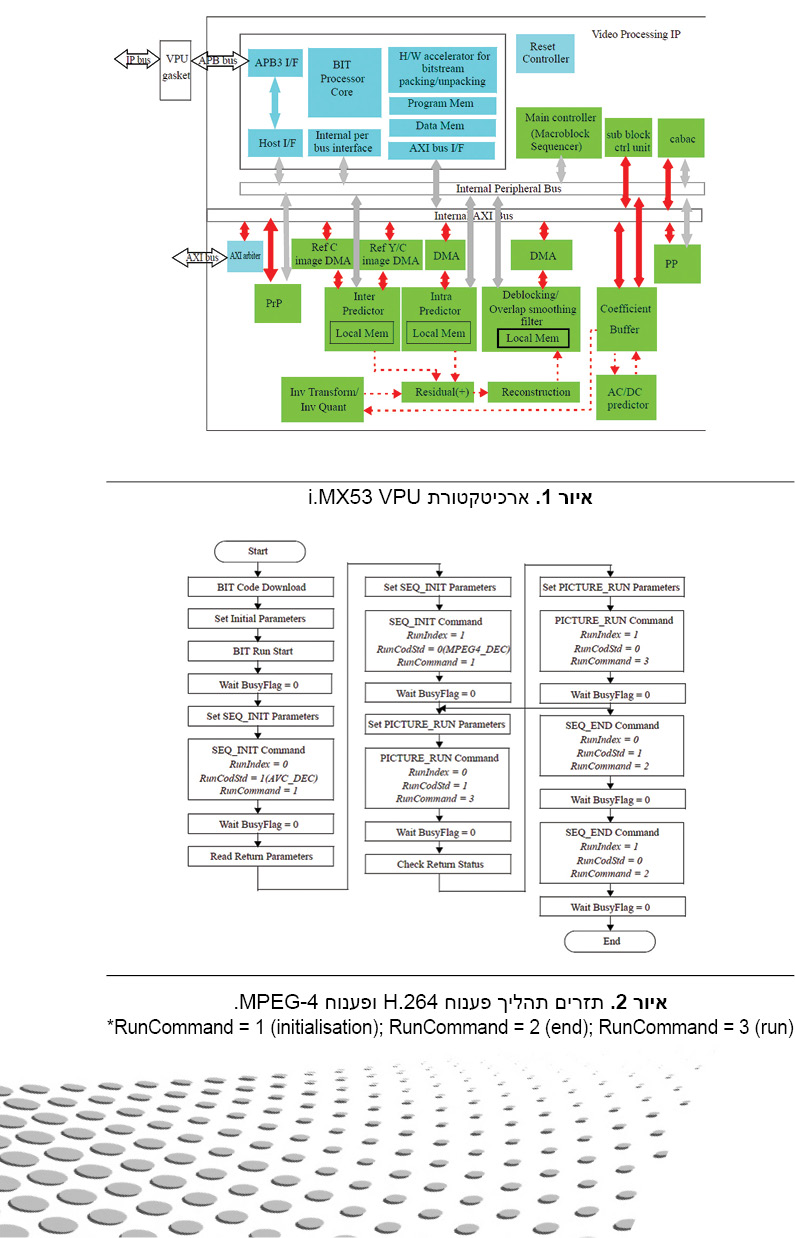

כמו רוב מאיצי חומרה, ל-VPU i.MX53 יש סדרה עשירה של תפקודי וידיאו מובנים. עם זאת, בשונה מרוב חומרות VPU, ה-i.MX53 מתוכן ליישום קל. מתן תצורת הפענוח/קידוד והממשק המארח, למשל, מבוצע דרך קושחה ב-DSP משובץ הניתן לתכנות והמכונה 'מעבד BIT' (ראה איור 1). זה מספק רמה של יכולת תכנות וגמישות בלתי רגילה.

והעתקת נתוני וידיאו ופקודות פנימה והחוצה מה-VPU גם היא קלה כי היא פועלת על שני ממשקים ברורים: ה-AXI וה-APB . ערוץ ה-AMBA3 APB של 32 סיביות (32-bit) מיועד לבקרת מערכת וה-AMBA3 AXI של 64 סיביות מיועד להעברת נתונים.

לבקרה פשוטה ויעילה של ה-VPU על ידי המעבד המארח, ה-VPU מספק רשמי ממשק מארח. רוב הפקודות והתגובות בין המעבד המארח לבין ה-VPU מועברות באמצעות רשמים אלה. לאמצעים מקיפים של בקרת ה-VPU, מסופקת גם סדרת תפקודי ממשק תכנות יישומים

(Applications Programming Interface – API) הכוללת את כל הפעולות הדרושות בצד המעבד המארח.

עם זאת, בפועל כמעט כל התפקודים, לרבות בקרת קצב Flexible Macroblock Order, Arbitrary Slice Ordering, בקרת פענוח/קידוד (codec) וידיאו וגמישות שגיאות (error resilience), מיושמות במעבד ה-BIT. זה אומר שהמשאבים הדרושים ל-CPU המארח על מנת לבקר את ה-VPU הנם מצומצמים וטיפוסית דורשים לא יותר מ-1MIPS של תפוקת עיבוד.

מרכיבים של ה-VPU i.MX53

ה-i.MX53 VPU מורכב משני רכיבים: codec וידיאו ו-VPU gasket. ה-codec וידיאו הנו הלב של מאיץ הוידיאו. הוא מורכב ממעבד ה-BIT של 16 סיביות, מחומרת codec וידיאו ומבורר/ממשק ערוץ.

ה-VPU gasket ממונה על הפיכת הערוץ AMBA APB3 לערוץ IP Sky Blue.

ה-VPU יכולה לטפל בארבעה תהליכים בו-זמניים לכל היותר. לכל תהליך יכולה להיות תבנית שונה – היא יכולה לטפל, למשל, בזרם סיביות MPEG-4, MPEG-2, H.264 ו-VC-1 זה לצד זה.

כל תהליך פענוח מורכב משלושה מרכיבים תפקודיים:

צור תהליך: התוכנה יוצרת ומעניקה תצורה לתהליכים.

הרץ תהליך: בזמן הנכון, התוכנה תתחיל תהליך מסוים. הזמן הנכון הנו כאשר הפענוח נמצא במצב סרק וזרם הסיביות אותו יש לפענח הנו זמין בזיכרון החיצוני.

נטוש תהליך: התוכנה נוטשת תהליך מסוים.

אם יש יותר מתהליך אחד המוכן להרצה, יש להקצות זהות (ID) תהליך שונה לכל אחד בתחום מ-0 עד 3, באמצעות תפקוד הנקרא RunIndex. הקצאת הזהות נעשית על בסיס סדר היצירה. למשל, כאשר תהליך פענוח MPEG-4 אחד, תהליך פענוח H.264 אחד, תהליך פענוח MPEG-2 אחד ותהליך פענוח VC1 אחד רצים בו-זמנית, ניתן להקצות את פענוח MPEG-4 למפתח (index) תהליך '0', את פענוח H.264 למפתח תהליך '1', את פענוח MPEG-2 למפתח תהליך '2' ואת פענוח VC1 למפתח תהליך '3'.

תהליך אחד אינו נוטל קדימות מאחר. לאחר יצירת כל התהליכים בשלב האתחול, המארח מאפשר למעבד ה-BIT לבצע את התהליכים המוגדרים ב-RunIndex. כל התהליכים מבוצעים במנגנון דמוי חלוקת זמן: אחרי שתהליך אחד מסיים לפענח מסגרת, ניתן לבצע את התהליך הבא.

איור 2 מציג דוגמה של תזרים תהליכים כזה, פענוח זרמי סיביות H.264 ו-MPEGבו-זמנית. ראשית נוצרים ומאותחלים שני תהליכי הפענוח, אחר כך כל תהליך מבוצע בתורו עם מתן פקודת "הרץ" (Run).

תזרים העבודה באיור 2 מורכב מהתפקודים הבאים:

1. אתחל את ה-VPU, לרבות:

הורד קוד BIT: הטען קושחת מעבד BIT בזיכרון.

קבע פרמטרים התחלתיים: תצורה כללית של מעבד ה-BIT, קביעת כתובת בסיס המאגר (buffer) הפעיל, כתובת זיכרון קוד ה-BIT, בקרת מאגר זרם הסיביות וכן הלאה.

התנעת ריצת ה-BIT: הרץ את מעבד ה-BIT לאתחול ה-VPU.

2. צור ואתחל תהליך פענוח:

תן תצורה לכתובת הבסיס ולגודל מאגר זרם הסיביות, לכתובת הבסיס של מאגרי מסגרת וכן הלאה.

התחל תהליך פענוח H.264.

בצע פעולה דומה עבור תהליך פענוח MPEG-4.

3. הרץ את תהליך פענוח ה-H.264:

תן תצורה לכתובת יעד המסגרת.

התחל את תהליך פענוח ה-H.264.

המתן עד שמעבד ה-BIT ישלים תהליך מסגרת אחת. המסגרת המפוענחת יכולה להישלח אל יחידת עיבוד התמונה

(Image Processing Unit – IPU) המשובצת של ה-i.MX53 לצורך עיבוד נוסף

(post-processing) ותצוגה.

בצע פעולה דומה עבור תהליך פענוח

ה-MPEG-4 וחזור עליה עד אשר כל המסגרות יעובדו.

4. הפסק את תהליכי העיבוד:

סיים כל תהליך ושחרר את כל משאבי הזיכרון.

תפקיד מכריע של ניהול זיכרון

לניהול זיכרון ב-VPU יש חשיבות מכרעת, מאחר שמטלות כמו פענוח 1080i/p צריכות רוחב סרט גבוה באופן קיצוני. לרוע המזל, לעתים רוחב הסרט של זיכרון הנו מאולץ, בייחוד במערכות המריצות מערכות הפעלה חדישות המתוכנות להיות מיטביות לרב-משימתיות.

אם הזיכרון הזמין ל-VPU הנו בלתי מספיק, התוצאה תהיה תצוגת וידיאו בלתי רציפה או אף שגיאות פענוח. ניהול קפדני של רוחב סרט הזיכרון יכול לסייע במניעת בעיה זאת.

ל-VPU יש גישה מוחלטת למלוא הזיכרון החיצוני, המשמש להטענה ולאחסון מסגרות תמונה, זרמי סיביות, תוכניות ונתונים עבור מעבד ה-BIT. הדרישה לגודל מאגר תלויה בתקן הוידיאו וביישום המטרה. למשל, פענוח H.264 יכול להשתמש בעד 16 מסגרות ייחוס. פענוח MPEG-4 ו-H.263 משתמש במסגרת ייחוס אחת בלבד. כל תקן דורש גם גודל שונה של זיכרון זמני כאשר הוא מעבד סינון de-blocking או החלקת-חפיפה (overlap-smoothing).

ה-VPU משתמש בשישה סוגי מאגר (buffer):

מאגר מסגרות, לאחסון מסגרות תמונה

זיכרון תוכנית מעבד BIT, לאתחול מחדש של קוד וקושחה

מאגר עבודה, לנתוני ביניים ממעבד ה-BIT וחומרת פענוח החוזי

מאגר זרם סיביות, להטענת נתוני זרם סיביות

מאגר פרמטרים, עבור טיעוני ביצוע פקודת מעבד ה-BIT ונתונים חוזרים

חיפוש RAM, בו משתמש מודול הזיכרון להפחתת עומס ערוץ SDRAM

המעבד המארח צריך להקצות מאגרים עבור זרמי סיביות על בסיס של כל מקרה לגופו. אם ה-VPU מטפל ב-n זרמי סיביות בו-זמנית ביישום, המארח אמור להקצות n מאגרים לזרמי סיביות ולהגדיר את כתובת הבסיס ואת הגודל.

יש עניין מיוחד במאגר זרם הסיביות החיצוני, אשר הנו מאגר טבעת. הכתובת ההתחלתית של מאגר הטבעת וגודל המאגר חייבים להיכתב על ידי המארח במעבד ה-BIT. כתובת הקריאה או הכתיבה השוטפת של מאגר הטבעת עטוף סביב אוטומטית על ידי קושחה.

במהלך הפענוח, המארח כותב את זרם הסיביות אותו יש לפענח ומעבד ה-BIT קורא אז את זרם הסיביות. במקרה זה, יתכנו כתיבת יתר (overwriting) או קריאת מאגר ריק (underflow); אם זה קורה, הפענוח ייכשל. על מנת למנוע כתיבת יתר או קריאת מאגר ריק, המחוון קריאה/כתיבה של זרם הסיביות השוטף חייב להתחלף בין המעבד המארח ומעבד ה-BIT. מעבד ה-BIT כותב את מחוון הקריאה השוטף של מאגר הטבעת ברשומה פנימית והמארח חייב לכתוב את מחוון הכתיבה השוטף של מאגר הטבעת ברשומה פנימית.

מעבד ה-BIT בודק את מצב ה'ריק' (underflow) של מאגר הסיבית על ידי השוואת מחוון הקריאה השוטף ומחוון הכתיבה. אם אין יותר נתוני זרם סיביות לפענוח (מצב מאגר ריק), מעבד ה-BIT מפסיק לפענח זרמי סיביות על מנת למנוע קריאה שגויה של זרם הסיביות וממתין עד אשר המארח יכתוב עוד נתוני זרם סיביות ויעדכן את מחוון הכתיבה. המארח חייב לבדוק את מחוון הקריאה ואת מחוון הכתיבה השוטפים לפני שהוא כותב עוד נתוני זרם סיביות במאגר הטבעת על מנת למנוע כתיבת יתר של נתוני זרם סיביות.

סיכום

אחד היתרונות הגדולים ביותר של השימוש במעבד עם VPU משובצת הנו בכך שתפקודים מוכנים מראש לפענוח ולקידוד וידיאו מיושמים בחומרה. ביצוע תפקודים אלה הנו עניין פשוט של קריאה לסדרת פקודות קטנה. במערכת מבוססת על DSP, תפקודים אלה חייבים להיכתב בתוכנה, אך ה-VPU מסתירה את המורכבות של התהליך מעיני המהנדס המתכן.

עם ה-VPU של i.MX53, Freescale עשתה עבודה טובה במיוחד של תמיכה במהנדס התיכון על ידי הענקת APIs פשוטים, תפקודים מאומתים באופן מלא וביצועים יציבים בזמן אמת. זה אומר שתכני מערכות חוזי המשתמשות בחומרת מאיץ ה-VPU של i.MX53 יכולה להיות מיושמת במהירות ויכולה להעניק ביצועי חוזי מצוינים.

ישראל שם-טוב: מהנדס יישומים מתקדמים, Future Electronics (ישראל)

הכתבה נמסרה באדיבות

(Future Electronics (EMEA ופריסקייל ישראל