Imec מגדירה מהם השלבים והרכיבים החיוניים למימוש טרנזיסטורים מונוליתיים מסוג CFET

- פיתוח תהליך לייצור אב טיפוס של טרנזיסטור מסוג מונוליתי מסוג CFET הוא לא דבר של מה בכך, בשל הצורך להפריד אנכית בין הטרנזיסטורים מסוג nMOS ו־pMOS מבלי להגדיל את השבב.

- בראיון זה, מסבירים האנס מרטנס, אן ואן דורן וסטיבן דמוינק – מהצוות המתמחה בטרנזיסטורים מסוג CFET ב־imec – כיצד הם מתקדמים בהתמדה לפתרון המורכבות הזאת.

- הם מתארים מהם תהליכי הייצור והרכיבים הנחוצים למימוש טרנזיסטורים מסוג CFET ומדגישים כי פיתוח טכנולוגיה ליצירת החיבורים בגב פרוסת הסיליקון, הוא המפתח להמשך מזעור התאים.

טרנזיסטורים מסוג CFET הם השלב הבא של ארכיטקטורת הננו־משטחים במפת הדרכים הטכנולוגית של תעשיית שבבי הלוגיקה

האנס מרטנס, חבר בכיר בסגל הטכני ב־imec מסביר: "כיום, תעשיית המוליכים למחצה נמצאת בעיצומו של מעבר מטרנזיסטורים מסוג FinFET לארכיטקטורת ננו־משטחים (Nanosheet), שתשמש כבסיס לדורות הבאים של שבבי הלוגיקה. ייתכן שבהמשך נציג פתרון המבוסס על ארכיטקטורת Forksheet, שהוצעה לפני שנים מספר. היא מבוססת על ארכיטקטורת הננו־משטחים, אך בשונה ממנה מאפשרת להגיע למרווחים קטנים יותר בין טרנזיסטורים סמוכים וכך להמשיך למזער את השבבים ולשפר את ביצועיהם לעומת ארכיטקטורת הננו־משטחים המסורתית. אנחנו צופים שטרנזיסטורים מסוג CFET ייכנסו למפת הדרכים הטכנולוגית לקראת סוף העשור הנוכחי. מכיוון שבארכיטקטורה הזאת מוצבים הטרנזיסטורים מסוג nMOS ו־pMOS זה על גבי זה, אין עוד צורך להפריד ביניהם, כך שאפשר להקטין את גובה התא. לצד פיתוחן של טכנולוגיות מתקדמות נוספות, שיאפשרו יצירת מגע בין הטרנזיסטורים האלה, תאפשר הארכיטקטורה הזאת את המשך מזעור גובה הרצועות מ־5T ל־4T והלאה, וכך למזער באופן משמעותי גם את גודל התא.

מנקודת מבט של תהליך הייצור, מדובר במשימה מורכבת, מכיוון שיש צורך למקם את הטרנזיסטורים מסוג nMOS ו־pMOS זה על גבי זה ואנחנו עדיין נמצאים בשלבים הראשונים של המחקר. הוצעו כמה שיטות לייצור טרנזיסטורים מסוג CFET, ובהן שיטת ייצור מונוליתית ולינארית. בתהליך ייצור ליניארי, כל הרכיבים מיוצרים על גבי מצעים נפרדים ואז מודבקים זה מעל זה לפי הסדר. בתהליך ייצור מונוליתי, נבנה הטרנזיסטור כולו באופן אנכי על גבי אותו מצע."

טרנזיסטורים מונוליתיים מסוג CFET: הדרך המהירה ביותר למימושם

אן ואן דורן, חברה בכירה בסגל הטכני ב־imec מסבירה: "בתחום שבבי הלוגיקה, מתמקדת פעילותה של imec ושותפיה בפיתוח שיטה לייצור טרנזיסטורים מונוליתיים מסוג CFET, מכיוון שהיא תאפשר לנצל חלק מהתהליכים והציוד המשמשים היום בייצור ננו־משטחים. אי לכך, הדעה הרווחת היא שזאת תהיה הדרך המהירה ביותר להגיע לייצור המוני של טרנזיסטורים מסוג CFET. עם זאת, כדי ליצור את המבנה האנכי שממנו ייוצרו שני סוגי הטרנזיסטורים, יש צורך בתהליך עם יחס צירים גבוה, השמת (ריבוץ) והסרת חומר סלקטיביות והשמת שכבות אפיטקסיאליות באיכות גבוהה. כמו כן, יהיה צורך לפתח רכיבים חדשים וייעודיים לתהליך הייצור של טרנזיסטורים מסוג CFET, שיאפשרו את הפרדה האנכית בשער ובאזור המגע.

הפתרון שלנו הוא לחלק את המחקר והפיתוח של טרנזיסטורים מונוליתיים מסוג CFET למיזמי ביניים ולעבור בהדרגה מהקל אל הכבד עד שנגיע לרמת המורכבות הנדרשת. כל מיזם ביניים כזה מבוסס על אב טיפוס שונה. השלב הראשון מתמקד בטרנזיסטורים מונוליתיים יוניפולריים מסוג CFET, שבהם מיוצרים התקני ה־p וה־n העליונים והתחתונים על גבי פרוסות סיליקון שונות. אבות הטיפוס הבאים יהיו מבוססים על טרנזיסטורים מונוליתיים מסוג CMOS CFET, שייוצרו על גבי אותה פרוסת סיליקון. ההבדל העיקרי בין השיטות הוא באופן חיבור הטרנזיסטורים מסוג CFET, כשהשאיפה היא להגיע לחיבור בתהליך middle-of-line (MOL) וליצור את החיבורים בגב פרוסת הסיליקון. תהליכים ושיטות שונות נבדקו עבור כל אחד מאבות הטיפוס, כשלכל אחד מהם יתרונות וחסרונות יחסיים בכל הנוגע לאיזון בין צריכת האנרגיה, הביצועים, גודל ההתקן ומורכבות התהליך. הידע והתובנות מהמחקר של כל אב טיפוס ישמשו אותנו במחקר של אב הטיפוס הבא בתור."

טרנזיסטורים מונוליתיים יוניפולריים מסוג CFET עם גודל שער 48 ננומטר

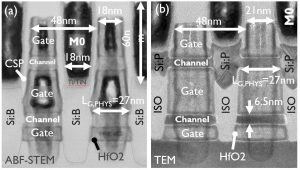

האנס מרטנס: "בכינוס VLSI 2020, הדגימה Imec בפעם הראשונה טרנזיסטורים מונוליתיים מסוג CFET על פרוסת סיליקון בקוטר 300 ננומטר, אם כי בגודל שער (CPP) גדול של 90 ננומטר. בכינוס VLSI 2023 שנערך השנה, הציגה Imec טרנזיסטורים יוניפולריים מסוג CFET עם גודל שער של 48 ננומטר, שכבר מתאים לייצור המוני [1]. עבודת המחקר הזאת נבחרה לאחד מההרצאות הבולטות בכינוס VLSI 2023. אבות הטיפוס שלנו הציגו יכולות אפיוני מיתוג יוצאות מן הכלל עבור התקני ה־nMOS וה־pMOS העליונים והתחתונים בנפרד. בימים אלה אנחנו עובדים על מציאת שיטות חדשות שיאפשרו להמשיך ולהקטין את גודל השער של הטרנזיסטורים המונוליתיים היוניפולריים מסוג CFET.

חתך רוחב של טרנזיסטורים מסוג (א) pFET תחתון ו־(ב) nFET עליון (LG,PHYS = 27 ננומטר) (התמונה הוצגה בכינוס VLSI 2023).

בהדגמה נבדקו המבנים האפיטקסיאליים של המקור־שפך והמגע מקור־שפך עבור הטרנזיסטור העליון או התחתון. כמו כן, כדי להגביל את יחס הצירים ולקצר את תהליך הפיתוח, החלק הפעיל של המבנה הוגבל רק לננו־משטח אחד עבור הטרנזיסטור התחתון וננו־משטח שני לטרנזיסטור העליון. כל זאת במטרה להדגים כי מצאנו דרך לשלוט בנפרד על ההתקן העליון והתחתון, באמצעות רווח של 30 ננומטר בלבד. זהו צעד חשוב בדרך לפיתוח תהליך ייצור מסחרי של טרנזיסטורים מסוג CFET."

טרנזיסטורים מונוליתיים מסוג CMOS CFET: האתגר הבא

סטיבן דמוינק, מנהל מדעי ב־Imec: "במקביל, אנחנו ממשיכים לעבוד על פיתוח אב טיפוס של טרנזיסטור מסוג CMOS CFET, שהוא יעד אסטרטגי עבור Imec ושלפיתוחו נרתמו שותפינו מהתעשייה. בשונה מטרנזיסטורים יוניפולריים מסוג CFET, יונח ההתקן מסוג n מעל ההתקן מסוג p על גבי אותה פרוסת סיליקון והם יחוברו בנפרד זה מזה. כמו כן, תהליך הייצור צריך לאפשר שימוש במתח סף (Vt) שונה בשני ההתקנים, אף על פי שהם חולקים שער משותף, וכל זה בגודל שער של 50 ננומטר המתאים לייצור המוני. המבנה האנכי הזה מציב לא מעט אתגרים. הוא מצריך לא רק פיתוח של שלושה תהליכים ייעודיים לטרנזיסטורים מסוג CFET, אלא גם שינויים בתהליך הייצור כולו, כדי להתאימו לרכיבים ולתהליכים החדשים.

הרכיב הייעודי הראשון לטרנזיסטורים מסוג CFET, שאותו אנחנו מכנים 'המבודד הדיאלקטרי האמצעי (Middle dielectric isolation או MDI בקיצור)', פותח בשל הצורך בשכבת בידוד דיאלקטרית אנכית בין חלקו העליון והתחתון של השער, כדי שתהיה אפשרות לשלוט בנפרד על מתח הסף (Vt) של הטרנזיסטור העליון והתחתון. לשם כך, הציע הצוות שלנו פתרון ייחודי שמשנה את תהליך הייצור כבר מהשלב הראשון: הפיכת מבנה הסיליקון (Si)/סיליקון־גרמניום (SiGe), המשמש ליצירת החלק הפעיל של הטרנזיסטור מסוג CFET, למבנה רב־שכבתי גבוה יותר המורכב משכבות Si/SiGe1/SiGe2, כאשר שיעור הגרמניום גבוה יותר בשכבת SiGe2 מאשר בשכבת SiGe1. בזמן ששכבות SiGe1 הדלות בגרמניום, שאותן אנחנו מקריבים, מוחלפות במתכות הסופיות שקובעות את מתח הסף (Vt), מומרות השכבות העשירות בגרמניום למבודד הדיאלקטרי האמצעי (MDI) ויוצרות את ההפרדה הנדרשת בין צד ה־n לצד ה־p של השער. המבנה הזה מאפשר ליצור את הריווח הפנימי בשכבה הדלה בגרמניום, שהוא מאפיין חיוני של ארכיטקטורת הננו־משטחים ותפקידו לבודד את השער מהמקור־שפך. כיום מתמקד המחקר שלנו במציאת הדרך היעילה ביותר לייצור המקור־שפך התחתון, שכבת הבידוד האמצעית החדשה והריווח הפנימי במרווחים זעירים וביחס צירים גבוה.

יש צורך בהפרדה אנכית נוספת בין המתכות שיוצרות את המגע בין המקור לשפך של הטרנזיסטורים העליון והתחתון. אנחנו חוקרים אפשרויות שונות ליצירת המגעים העליון והתחתון ובידודם, למשל על ידי הכנסתם עמוק בין שני שערים גבוהים, ובהמשך יצירת חיבור בין הטרנזיסטורים העליון והתחתון. בכינוס VLSI 2023 הצגנו הוכחת היתכנות של תהליך המבנה הזה בשיטת שלב ה־MOL [2].

ולבסוף, נצטרך למצוא דרך לעטוף את הערוץ העליון בשעת גידול המבנה האפיטקסיאלי של המקור־שפך בטרנזיסטור התחתון. ברגע שנשיג זאת, נוכל לגדל מבנה אפיטקסיאלי בדרגות אילוח שונות עבור הטרנזיסטורים העליון והתחתון.

יצירת חיבורים בצידם האחורי של מעגלי CFET

אן ואן דורן: "בטווח הארוך, מתמקד המחקר שלנו בחיפוש שיטות מתקדמות לחיבור ההתקנים הפעילים דרך צידו האחורי של פרוסת הסיליקון. הסיבה לכך היא הצורך להמשיך ולהקטין את גובה התא ולהימנע מגודש מסלולים בצידה הקדמי של פרוסת הסיליקון.

יצירת החיבורים בצידה האחורי של פרוסת הסיליקון מוסיף שלבים ומורכבות לתהליך, כמו למשל חיבור פרוסת הסיליקון ואיכולה מצידה האחורי. אלה שלבים מאתגרים, בשל הגודל המזערי שמקשה ליישר את השכבות בגב פרוסת הסיליקון עם המבנים הקטנים שכבר קיימים בצידה הקדמי. האתגר הופך למורכב עוד יותר כשנוצרים עיוותים בפרוסת הסיליקון במהלך החיבור, המחייבים שימוש בשיטות תיקון מיוחדות. כמו כן, יש צורך בפיתוח של רכיב חדש שיספק בידוד מתאים בין שכבת המתכת הראשונה בגב פרוסת הסיליקון והננו־משטח הפעיל של ארכיטקטורות CFET."

טרנזיסטור מסוג CFET: גם התעשייה נרתמת

סטיבן דמוינק: "בזמן שחלף מאז שהתחלנו במאמצי המו"פ של טרנזיסטור מסוג CFET, גדל מאוד העניין מצד ספקי הציוד שלנו. מצד אחד, הם רוצים להיות מעורבים כבר בשלבים מוקדמים, כדי להבין כיצד משתלבים הכלים, התהליכים והחומרים שלהם במפת הדרכים הטכנולוגית. הם גם רוצים להבין את תהליך הייצור, כדי שיוכלו להיערך בהתאם. Imec מספקת להם פרוסות סיליקון מתאימות שעליהן כבר נמצאים המבנים הנחוצים לארכיטקטורת CFET. זהו חידוש מכיוון שבדרך כלל אין ליצרנים גישה מוקדמת לפרוסות סיליקון כאלו עד לתחילת הפיתוח ב־IDM. מאידך, שיתופי הפעולה האלו תורמים רבות גם ל־Imec. שיתוף הפעולה עם ספקי הציוד מעניק לנו גישה ליכולות החדשות ביותר.

בד בבד, גם יצרני שבבי הלוגיקה שאיתם אנחנו עובדים מתעניינים באתגרים שבהם נתקלנו ובתובנות שלמדנו. הבנה מוקדמת של הציוד והתהליכים הנחוצים להצלחת התהליך מאפשרת ליצרנים להיערך מבעוד מועד ולהתחיל במאמצי מחקר ופיתוח משלהם."

רוצה לדעת עוד?

[1] ‘Nanosheet-based complementary field-effect transistors (CFETs) at 48nm gate pitch, and middle dielectric isolation to enable CFET inner spacer formation and multi-Vt patterning’, H. Mertens et al., VLSI 2023;

[2] ‘Integration of a stacked contact MOL for monolithic CFET’, V. Vega-Gonzalez et al., VLSI 2023.

על מחברי המאמר

משמאל לימין: סטיבן דמוינק, מנהל מדעי ב־Imec; אן ואן דורן, חברה בכירה בסגל הטכני ב־imec; האנס מרטנס, חבר בכיר בסגל הטכני ב־imec.קרדיט: IMEC

סטיבן דמוינק מחזיק בתואר M.Sc בפיזיקה מאוניברסיטת לוון (1994) ובתואר Ph.D בפיזיקה מאוניברסיטת לוון בשנת 2000. הוא הצטרף ל־Imec בשנת 2001 וכיום מכהן כמנהל המדעי. במסגרת תפקידו, הוא מוביל את המחקר והפיתוח של אב טיפוס של טרנזיסטור מונוליתי מסוג CMOS CFET על Sigma2.

לאן ואן דורן תואר M.Sc בהנדסת חשמל מאוניברסיטת לוון (1996) ותואר Ph.D בהנדסת חשמל מאוניברסיטת קליפורניה בדייוויס (2000). בין השנים 2000 ל־2007, היא עבדה כחוקרת בכירה במוטורולה/פריסקייל סמיקונדקטור, שם עסקה בתהליכי ייצור של טכנולוגיות FDSOI ו־FinFET. היא הצטרפה ל־Imec בשנת 2007 וכיום היא מכהנת כחברה בכירה בסגל הטכני. במסגרת תפקידה היא עוסקת בפיתוח ארכיטקטורות חדשניות של טרנזיסטורים מסוג CFET, ובהן ארכיטקטורה מונוליתית ולינארית, וכן בשיטות ליצירת החיבורים בגב פרוסת הסיליקון.

האנס מרטנס הוא בעל תואר M.Sc בפיזיקה יישומית מאוניברסיטת איינדהובן לוון (2002) ותואר Ph.D בפיזיקה מהאוניברסיטה הטכנית של איינדהובן (2007), שתיהן בהולנד. בין השנים 2007 ל־2012 הוא עבד כמדען בכיר בחברת NXP Semiconductors, שם עסק בעיקר בפיתוח טרנזיסטורים ביפולריים מסוג SiGe, עם צומת הטרוגנית ליישומי תקשורת אלחוטית. הוא הצטרף ל־Imec בשנת 2012 וכיום מכהן כחבר בכיר בסגל הטכני. הוא עוסק במציאת שיטות חדשות לייצור ארכיטקטורות מתקדמות של טרנזיסטורים מסוג CMOS, ובהם טרנזיסטורים מסוג CFET.