בראשון בחודש יולי 2015 הכריזה חברת Xilinx על יצור (Tape Out) משפחת הדור החדש בסדרת רכיבי המערכות על שבב ( – System On Chip). המשפחה החדשה, Zynq UltraSscale+ Mpsoc, מציעה קפיצת מדרגה של מעל לפי 5 ביחס ביצועים/צריכת הספק ביחס למשפחת ה-Zynq SoC המיוצר בטכנולוגיה של 28 ננומטר. בעוד Xilinx הייתה יכולה ליישם את הדור השני של משפחת ה-SoC שלה בתהליך 20 ננומטר של TSMC, החברה בחרה להמתין ליישום ההתקן בתהליך FinFET בטכנולוגיית 16 ננומטר במפעלי . Xilinx תכננה רכיב הטרוגני ומרובה ליבות המשלב ריבוי ליבות מתחומים שונים לבין ארכיטקטורת ה-UltraScale של החברה, דבר שיביא למערכת עיבוד מרכזית יעילה במיוחד.

חשוב להבהיר שלמרות שכבר בטכנולוגיית ה-20 ננומטר שלה חשפה Xilinx את ארכיטקטורת ה-UltraScale, בטכנולוגיית ה- 16 ננומטר חשפה החברה את הדור הבא של הטכנולוגיה הנקראת UltraScale ().

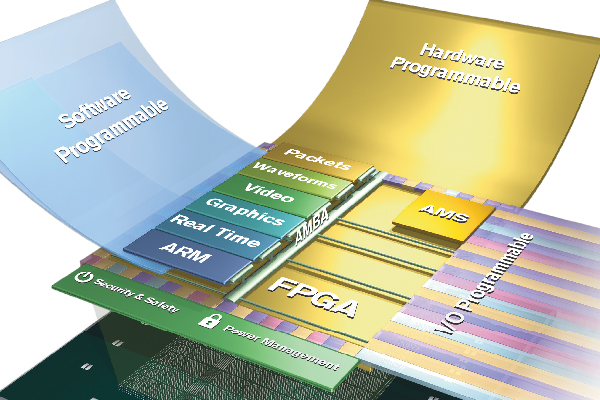

במהלך השנה שעברה (2014) חשפה Xilinx את אסטרטגיית ה”המנועים הנכונים למשימות הנכונות” (“Right Engines for the Right Tasks”) לארכיטקטורת UltraScale MPSoC, אולם היא הסתירה את מרבית הפרטים בדבר אילו ליבות יהיו בשימוש בארכיטקטורת ה-Zynq UltraSscale+ Mpsoc. בתחילת שנת 2015 ביצעה החברה חשיפה מלאה לתכונות ומאפייני המשפחה החדשה (ראה איור 1). ידוע כי הערך המוסף הגדול ביותר של רכיבי ה-Zynq SoC המקורי בטכנולוגית 28 ננומטר היה בשילוב מערכת עיבוד של ARM וחומרה מתכנתת ברכיב אחד. ברכיב זה יותר מ-3,000 חיבורים (המאפשרים רוחב פס שיא של עד Gbps ) המקשרים בין מערכת העיבוד של Zynq SoC לבין הלוגיקה המתכנתת. חיבור הדוק זה בין ה-PS () לבין ה-PL () מפיק ביצועים מעל ומעבר לכל ארכיטקטורה מבוססת שני שבבים של FPGA ו-ASSP בנפרד. כעת עם יישומו של רכיב ה-UltraScale בטכנולוגיית ה-16 ננומטר הגדילה Xilinx באופן דרמטי את הביצועים בין מערכת העיבוד (PS) לבין מערכת החומרה המתכנתת (PL). בדור החדש יותר מ-6,000 חיבורים הפועלים ברוחב פס שיא של 500. הדבר הופך את הקשר בין מערכת העיבוד (PS) ומערכת החומרה המתכנתת (PL) של מערכת

ה-Zynq UltraScale+ MPSoC למהירה פי שש (6X) מאשר הדור הקודם של ה-Zynq SoC שבוסס על 28 ננומטר. כעת המשפחה החדשה משאירה את ארכיטקטורות ASSP בתוספת FPGA הרחק מאחור במונחי ביצועי מערכת. מרכז ה-Zynq UltraScale+ MPSoC הינו יחידת עיבוד בעלת ארבע ליבות מבוססת ARM Cortex-A53 בעלת 64 סיביות, המספקת יותר מכפול ביצועים בהשוואה למערכת העיבוד הכפול מסוג Cortex-A9 של Zynq SoC בטכנולוגיית 28 ננומטר. מערכת העיבוד החדשה (A53) מסוגלת לווירטואליזציה מלאה של חומרה ועיבוד א-סימטרי (AMP) ותומכת בחבילת ®TrustZone של חברת ARM של המאפשרת תכונות אבטחה באופן מלא. ברכיב ה-Zynq UltraScale+ MPSoC הלכה Xilinx צעד נוסף לעומת הדור הקודם ויישמה מערכת עיבוד נוספת מסוג ARM Cortex-R5 בעלת ליבה כפולה. מערכת משנה זו, הינה מערכת עיבוד בזמן אמת (Real Time) המאפשרת למשתמשים להוסיף פעולה דטרמיניסטית למערכות שלהם. המעבד בזמן אמת מבטיח היענות מערכת מידית ליישומים שדורשים את הרמות הגבוהות ביותר של תפוקה, בטיחות ואמינות.

ה-Zynq UltraScale+ MPSoC כולל גם מספר המנועים גרפיים ייעודיים לצורך ביצועי עיבוד נוספים. ליבת ההאצה הגרפית ייעודית מסוג ARM Mali™-400MP עתירת ביצועים מורידה עומס מהמעבד הראשי כאשר יש צורך במשימות עיבוד גרפי. כדי להשלים את יכולות העיבוד הגרפיות, הוסיפה Xilinx ליבת קידוד ופריסה לווידאו (Codec) הנמצאת בלוגיקה המתכנתת. בלוק זה, שהינו מוקשח ברכיב (hardened) מאפשר דחיסה ופריסה של וידאו בתקן H.265 ותומך בתקן 8K4K בקצב של 15 מסגרות לשנייה ובתקן 4K2K בקצב של 60 מסגרות לשנייה. ליבה נוספת שהוקשחה ברכיב הינה ממשק DisplayPort המאפשר למשתמשים להאיץ הוצאת וידאו מהרכיב ללא צורך בשבב חיצוני נוסף. רכיב ה-Zynq UltraScale+ MPSoC כולל גם מספר שיפורי זיכרון פנימי בהשוואה לדור הקודם. המכשירים הגדולים ביותר במשפחת המוצרים יכללו Ultra-RAM בנוסף לבלוק זיכרון BRAM הנמצאים בלוגיקה המתכנתת. ליבות עיבוד Zynq UltraScale+ MPSoC יכילו זיכרונות מטמון מסדר ראשון וסדר שני (L1 & L2 Caches) משופרים. הזיכרון הנדיף מחוץ לרכיב יכלול כעת ליבה רחבה יותר של עד 72 סיביות (64 סיביות מידע בתוספת 8 סיביות ECC). הממשק מתגאה במהירויות של עד Mbps 2,400 להתקני DDR4, עם תמיכה בעומק זיכרונות DRAM גדול בהרבה מהדור הקודם המגיעים עד 32 ג’יגה בייט.

יחידת אבטחה ייעודית ב-Zynq UltraScale + MPSoC מאפשרת אבטחה בתקנים צבאיים כגון אתחול מאובטח, ניהול מרכזי וכספת (Vault) ויכולות מניעת חבלה/פריצה. יכולות אלו הן היום דרישות רגילות ליישומי בקרה וכן למערכות תקשורת מסוג מכשיר למכשיר/מחשב (Machine-to-Machine). בנוסף, המערכת כוללת גם התקני קישוריות מוקשחים עבור , , וPCIe Gen4-. הרכיב משלב גם ליבה לאותות אנאלוגיים (Analog Mixed-Signal -) המסייעת בבדיקת המערכת במעבדה וכן בזמן אמת ע”י מדידות שונות כגון: טמפרטורה, ממתח וכדומה.

עם כל התכונות הללו, אין זה סביר כי מערכת מסוימת תזדקק להשתמש בכל המנועים הזמינים ב-Zynq UltraScale+ MPSoC. לכן תכננה Xilinx בתוך הרכיב יחידת בקרה וניהול הספק וממתחים ( – Power Management Unit) גמישה ביותר לניהול ושליטה ברכיב. הליבה מאפשרת למשתמש לשלוט ולספק ממתח רק לבלוקים שבשימוש המערכת בצורה מתוחכמת וממוקדת (fine-grained). מעבר לכך, יחידת בקרת ההספק מאפשרת למשתמשים דינאמיות, כדי להבטיח כי המערכת מפעילה רק את התכונות דרושות לביצוע משימה נתונה בזמן נתון ולאחר מכן מכבה תכונות אלו. יחידת ניהול זו מבצעת גם בקרה של בטיחות ואמינות כגון זיהוי טעויות מערכתיות ושיכוכן (error detection and mitigation), יכולת מצב בטוח (safe-state mode) יכולות בידוד (isolation) והגנה (protection).

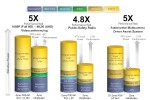

התכונות שנדונו לעיל, בתוספת לחסכון בהספק שמביאה טכנולוגית ה-FinFET של 16 ננומטר מעניקים לרכיבי ה-Zynq UltraScale+ MPSoC את היכולת לספק יתרון של פי 5 (5X) ביחס ל-Zynq SoC מטכנולוגיית ה-28 ננומטר. לצורך התרשמות מביצועי Zynq UltraScale+ MPSoC בדבר היתרון ביחס ביצועים/הספק, נתבונן באיור (איור 2) הסוקר ביצועים והספק עבור שלוש מערכות מתחומים שונים: תחום שיחות וידאו, מערכת רדיו מתחום בטחון הציבור ומערכת עזרה לנהג ברכב בסביבה רווית מצלמות. כמובן שאלו רק דוגמאות אולם בכולן ניתן לראות את שילוב תחומי החומרה, התוכנה, זיכרונות, ממשקים חיצוניים ולעיתים אף גרפיקה, וידאו ועיבוד בזמן אמת. מהאיור ניתן לראות כי המשפחה החדשה פותחת במפני המשתמשים עולם חדש של יכולות מערכת.

- איור 1. מאפייני משפחת רכיבי ה- Zynq UltraScale+ MPSoC

- איור 2. השוואת ביצועי הדור החדש בטכנולוגיית 16 ננומטר לעומת הדור הנוכחי בטכנולוגיית 28 ננומטר