מאת: אבי פנקס, פיניקס טכנולוגיות בע"מ. שני פיתוחים חשובים מסעירים כיום את עולם רכיבי ה-FPGA: הופעתם של רכיבים מתכנתים בטכנולוגיית 22 ננומטר וזמינותם של רכיבים שמותאמים

מאת: אבי פנקס, פיניקס טכנולוגיות בע"מ. שני פיתוחים חשובים מסעירים כיום את עולם רכיבי ה-FPGA: הופעתם של רכיבים מתכנתים בטכנולוגיית 22 ננומטר וזמינותם של רכיבים שמותאמים

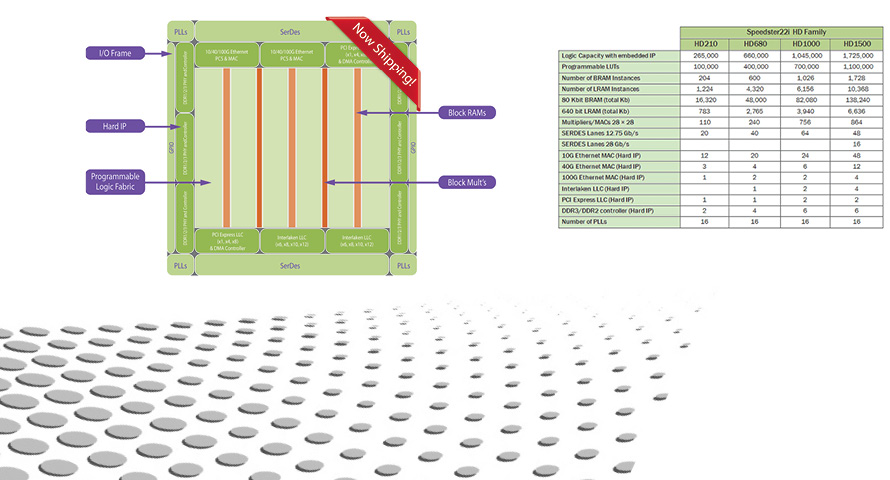

במיוחד לשווקים ספציפיים – באמצעות שימוש בנכסים רוחניים המובנים בחומרה (Hard IPs). פיתוחים אלו מיושמים ברכיבי ה-FPGA ממשפחת Speedster22i של Achronix Semiconductor, אשר משתמשים ומספקים מגוון רחב של נכסי IP המובנים בחומרה.

טכנולוגית ייצור חדשה: Tri-Gate, ננו-מטר

כל רכיבי ה-Speedster22i נהנים מהיתרונות של השימוש בטכנולוגיה של 22 ננו-מטר של Intel. היתרונות הברורים ביותר הם היתרונות שנובעים כתוצאה משימוש בטכנולוגיה חדשה:

א. צפיפות גבוהה יותר (ומכאן עלות נמוכה יותר לכל פונקציה לוגית)

ב. ביצועים גבוהים יותר

ג. צריכת הספק נמוכה יותר (לכל פונקציה לוגית)

בנוסף ליתרונות מוכרים אלו, הטכנולוגיה של 22 ננו-מטר של Intel, מביאה עמה חידוש מהפכני במבנה הטרנזיסטור המשלב בתוכו Tri-Gate או בשמו האחר FinFET. במבנה זה של טרנזיסטור, מבנה השער (gate) התלת ממדי מקיף את הערוץ והתוצאה המתקבלת היא בקרה טובה יותר מאשר הבקרה במבנה הרגיל של הטרנזיסטור השטוח (בזכות אזור המשטח הגדול יותר שבין השער לערוץ). צריכת ההספק הסטטית (הידועה גם כזליגה) הנגזרת מחוסר היכולת לסגור לחלוטין את הטרנזיסטור, הלכה וגדלה במשך השנים. הרכיבים צורכים הספק במידה רבה גם כאשר אין הם מבצעים דבר! – מעתה, סוף כל סוף, הבעיה נפתרה.

התמקדות חדשה

ראינו כבר שלמרות היתרונות הרבים של רכיבי FPGA על פני רכיבי ASIC, (בהם נכללים זמן יציאה קצר יותר לשוק, עלות כוללת נמוכה יותר, יכולת עדכון בשטח ועוד), רכיבי ה-FPGA סבלו מתופעת "האולר השוויצרי" – כלומר יכולתם לתת מענה למגוון רחב של יישומים, עם זאת, ללא כל הצטיינות בתחום אחד מסוים. רכיבי Speedster22i עונים לחסרון זה על ידי התמקדות ישירה בקבוצה מוגדרת של תחומי שוק. בלוקים מורכבים של נכסי IP מובנים בחומרה משולבים בתוך הרכיבים באמצעות טכנולוגיית "התא הסטנדרטי" (כלומר רכיב ASIC). תכנונים של יישומים שמשתמשים במידה רבה בבלוקים אלו של נכסי IP בחומרה הם המרוויחים העיקריים של התמקדות זו.

בלוקים אלו של נכסי IP בחומרה כוללים בקרים של 1,10G/40G/100G Ethernet Interlaken ו-PCI-Express וכן בקר זיכרון DDR3. פונקציות אלו מומשו בעבר באמצעות ה-FPGA’s programmable fabric – בזבוז של משאבי ליבה יקרי ערך, שאותם יש לשמור לפונקציות ייחודיות למשתמש ולא להשתמש בהם לפונקציות סטנדרטיות. שימוש של נכסי IP בבלוקים מובנים בחומרה אלו מספקת יתרונות עצומים:

א. זמן תכנון מקוצר (אין צורך

ב-timing-closure עבור בלוקים אלו, הם כבר פועלים ברמת הביצועים הנדרשת)

ב. צריכת הספק מופחתת

ג. ביצועים משופרים

ד. יחס עלות / שטח מוקטן

ה. אין תשלום עבור רישיון שימוש.

חשוב לציין שאפילו יישומים שאינם משתמשים אף באחד מבין הבלוקים האלו, זוכים מהיתרונות של טכנולוגית FinFET ב-22 ננו-מטר.

הרכיב הראשון

הרכיב הראשון ממשפחת Speedster22i, הזמין כיום, הוא HD1000.

התכונות החשובות של הרכיב HD1000 הן:

700,000

זיכרון RAM בגודל של 86 מיליון-סיביות

756 בלוקים של צבירה וכפל

(multiply-accumulate)

64 נתיבי מקמ"ש (SerDes Transceivers) (בקצב של 1 עד 12.75 ג'יגה סיביות בשנייה)

שני בקרי Ethernet MAC בקצב של 100G בנכסי IP מובנים בחומרה (שניתן גם להגדיר אותם בקונפיגורציה לשישה בקרים בקצב של 40G או כעשרים וארבעה בקרים בקצב של 10G)

שני ממשקי Interlaken מובנים כנכסי IP בחומרה ל-100 ג'יגה סיביות בשנייה

שני ממשקי PCI-Express דור 3 מובנים כנכסי IP בחומרה

שישה בקרי זיכרון DDR3 ב-72 סיביות ל-2.133 ג'יגה סיביות בשנייה מובנים כנכסי IP בחומרה.

חשוב לציין שאפשר לבצע מעקף באופן מלא על כל בלוק של נכס IP מובנה בחומרה שלא נמצא בשימוש – כך שהכניסות והיציאות (IO) הקשורות או נתיבי SerDes הקשורים ניתנים לשימוש בכל מקרה.

כמו כן ניתן להזמין פלטפורמת פיתוח רבת יכולת שניתנת לחיבור באמצעות ממשק PCI-Express וכוללת בתוכה את הרכיב HD1000. השילוב של הרכיב HD1000 עם ערכת הפיתוח מדגים באופן משכנע את העליונות של קו מוצרי Speedster22i ביישומי תקשורת. זמן קצר אחרי יציאתם לשוק של מוצרים אלו יופיעו מוצרי Speedster22i נוספים במגוון של גדלים ויכולות (כפי שניתן לראות בטבלה). כל אלה יכללו כמובן את היתרונות הבסיסיים של המשפחה – בהתבסס על הטכנולוגיה ועל נכסי IP בחומרה.

רוחב פס: נתונים וזיכרון

רוחב פס היא דרישה חשובה שמעמידים שווקי היעד. רכיבי Speedster22i מספקים את רוחב הפס הזה בשתי צורות – בהתבסס על כניסות ויציאות ובהתבסס על מקמ"ש (transceiver).

הכניסות והיציאות הניתנות לתכנות של התקני Speedster22i – אשר פותחו על ידי Intel – תואמים בין היתר לתקני LVCMOS HSTL ,SSTL ו-LVDS והם בעלי יכולת רבה במיוחד עבור יישומים של ממשקי DDR3 שבהם נתמכים קצבי נתונים של 2.133 ג'יגה סיביות בשנייה. כך, כל ממשק לזיכרון DDR3 של 72 סיביות מספק יותר מ-150 ג'יגה סיביות בשנייה של רוחב פס לזיכרון (יותר מ-900 ג'יגה סיביות בשנייה, כאשר כל ששת הממשקים נמצאים בשימוש).

רוחב הפס העיקרי להעברת נתונים מסופק על ידי שישים וארבעה מקמ"שי SerDes, שפועלים על פני טווח קצבים מ-1 עד 12.75 ג'יגה סיביות בשנייה. הארכיטקטורה שלהם, הספרתית לחלוטין, מובילה לעליונות על פני כל הרכיבים האחרים הקיימים בעולם רכיבי ה-FPGA.