מאת: רונן סטילקול, ANSYS ISRAEL.

אימות תכנון רשת אספקות המתח לרכיבי הסיליקון בתכנון “System On Chip” נחשב לאתגר שכן אין סטנדרט בתעשייה שניתן לפעול לפיו וכך תתקבל רשת אספקות מתח מתאימה לצריכת הזרם של המעגל. בתחומים אחרים ישנה תכנית אימות עם בדיקות רבות שלאחר ביצוען בהצלחה התכנון נחשב לבטוח וניתן להמשיך לייצור "TAPEOUT".

היכולת להשיג כיסוי גבוה בבדיקת רשת אספקות המתח של הרכיב משמעותה שהתכנון לאחר הייצור אינו חשוף לכשל לוגי בשל מסלול קריטי שהופר או תכנון אנלוגי שהפך לא תקין מפאת רמת רעש ספקים גבוה מעבר למפרט שלו. היבט כישלון נוסף הוא הפרת ריצוד שעון

ה- (JITTER) אשר יכול לגרום לכשל לוגי, אבל לפני כן לאי עמידה בדרישות התכנון ביציאת שעון ה-DDR של השבב.

במאמר זה נציג את תהליך האימות של רשת אספקות המתח לרכיבי הסיליקון בעל כיסוי אימות גבוה תוך שמירה על מאמץ נמוך ומציאת נקודות התכנון החלשות בתחילת מחזור התכנון.

תהליך אימות רשת אספקת המתח

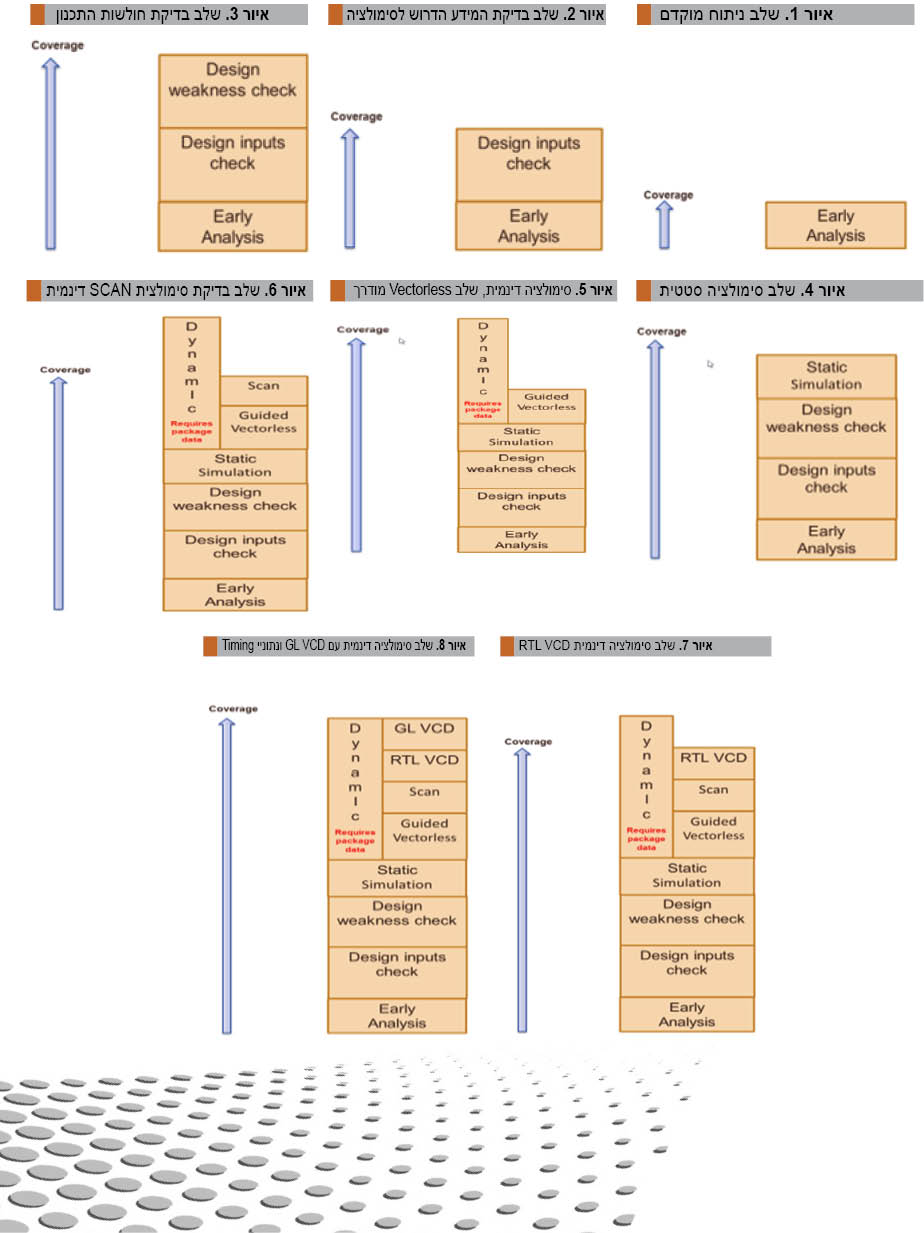

הכיסוי גבוה באימות רשת אספקת המתח לרכיבים במאמר זה כולל שמונה שלבים, כל שלב מגדיל את כיסוי האימות. מומלץ לבצע את כל השלבים ולפי הסדר הנכון. להלן תיאור של כל שלב ותרומתו לכיסוי הסופי.

שלב תכנון מוקדם

בשלבים מוקדמים של התכנון מומלץ להשתמש באב טיפוס מוקדם של רשת אספקת המתח בשילוב עם הערכת הספק מוקדם מסימולצית RTL, השגת אב טיפוס של רשת אספקת המתח העומד בדרישת התכנון יכולה למנוע שינויי תכנון גדולים מאוחר יותר במחזור התכנון.

השלבים הבאים קשורים לתכנון backend זמין

שלב בדיקה: האם התכנון נקרא כראוי

על כל חלקיו?

שלב שני הוא כדי לוודא כי נתוני התכנון נקראו כולם כראוי, אם חלק מנתוני התכנון חסרים, התוצאות המתקבלות יכולות להיות לא רלוונטיות.

בשלב זה, כל נתוני הקלט של התכנון לסימולציה מאומתים, מידע חסר מדווח עם כמותו, ניתן להשתמש באמצעי זה ולסדר עדיפויות בעת השלמת הנתונים החסרים.

בנוסף, הגדרות הסימולציה נבדקות והמתכנן מקבל דו"ח לתיקונים נדרשים, מספר דוגמאות הן: התקנים חסרים בספריות, ותדירות הסימולציה הנדרשת להשגת הערכה טובה של הספק התכנון.

שלב בדיקת

חולשות התכנון

מציאת חולשות התכנון נעשה לאחר קריאת נתוני התכנון וחילוץ ערכי ההתנגדויות בכל נקודה ברשת האספקות. ניתן לפתור בעיות רבות בשלב זה כולל מציאת חסר ב-vias, איתור קצרים וגילוי של קווים מנותקים.

מבחן מיוחד בשלב זה, הוא לבדוק את האיכות של רשת אספקת המתח, LVS בודק את קיומו של חיבור חשמלי אך אנו צריכים לבדוק את איכות החיבור, התנגדות רשת אספקת המתח לכל רכיב מדווחת, התנגדות גבוהה תקטין את החסינות לרעש ויכולה להצביע על סיכוי ל-DROP גבוה. פתרון חיבור התנגדות גבוהה לרכיב בשלב זה יחסוך זמן רב בניפוי שגיאות בלתי נחוצות בשלבים הבאים.

שלב בדיקת

הסימולציה הסטטית

שלב סימולציה סטטית הוא הסימולציה המומלצת הראשונה, שלב זה חיוני כדי למצוא בעיות ממוצעות אבל לא מסוגל ללכוד השפעות דינמיות כמו:

השפעת השראות האריזה

השפעת קיבולים פרזיטים ומתוכננים Decaps

השפעת מיתוג בו זמני של רכיבים

במהלך שלב זה ובשל האופי הממוצע של סימולציה זו, הכיסוי הוא גדול בעיקר בשל ההתייחסות לגורמים הבאים:

1. צפיפות המתכות בתכנון נאותה לתכנון צריכת אספקת הזרם הממוצע.

2. מספר ה-PAD’s/BUMP מתאים לצריכת הזרם המרבי.

3. במידה והתכנון כולל שערי אספקות מתח (power gates), מתבצעת בדיקה שמספרם יכול להזין את ממוצע הזרם הדרוש לרכיבים ללא DROP גדול.

סימולציה דינמית, שלב הרצת vectorless מודרך

בעת מעבר מסימולציה סטטית לדינמית חשוב מאוד לכלול את נתוני האריזה, השראות גבוהות באריזה יכולות להגדיל את ה-IR DROP הדינמי באופן משמעותי.

הסימולציה הדינמית הראשונה המומלצת היא Vectorless, למרות שהיא לא כוללת מידע מיתוג מדויק, תוך שימוש בבחירה נכונה של רכיבים מתמתגים כדי ליצור צריכת זרם רגעית מקסימאלית. הבחירה נעשית על פי הקריטריונים הללו: בהתחשב בכל מופע: פונקציה לוגית של הרכיב, Toggle, זמן מיתוג החופף לרכיבים אחרים, עצמת הזרם הדרושה למיתוג, תדירות וחולשת החיבור לרשת אספקת המתח.

הסימולציה Vectorless היא חשובה ביותר עבור כיסוי אימות מקסימלי בכדי למצוא את נקודות התורפה של התכנון.

סימולציה דינמית, שלב Vectorless מונחה

Vectorless מונחה הוא כאשר ישנה הוספת מידע על אופי מיתוג הרכיבים והספקם בכדי לקבל סימולציה מציאותית יותר.

סימולציה דינמית, שלב בדיקת SCAN

בדיקת ה-SCAN משקפת את שיא צריכת הזרם בסימולציה דינמית, במקרה זה כל ה-FF’s מקבלים אותו תדר השעון והקישוריות הלוגית נעשית באמצעות ממשקי SCAN SI/SO.

את הסימולציה ניתן לבצע במצב Vectorless כאשר דוח ATPG

מספק מידע על מבנה ה-SCAN.

סימולציה דינמית, שלב RTL VCD

RTL VCD לא תמיד זמין במהלך זמן התכנון, שימוש בו יכול ליצור תרחיש מיתוג מציאותי יותר אבל מוגבל לוקטורים ספציפיים שאינם מכסים את התכנון המלא, במקרה זה ניתן להשתמש ב-Event/State propagation וחישוב ההספק יהיה מדויק יותר, זמני המיתוג עדיין נלקחים מנתוני STATIC TIMING ועיתוי המיתוג משקף את המקרה הגרוע ביותר.

סימולציה דינמית, שלב VCD עם GL Timing

התועלת ב-RTL VCD לעומת GL VCD היא בגודל של קבצי ה-VCD.

VCD GL כולל מידע מדויק של זמן מיתוג הרכיבים בסימולציה, סימולציה זו היא מאוד מדויקת ומשולבת עם מידול מדויק של צריכת הזרם של הרכיבים APL והשפעת האריזה תוך שימוש ב-TIME STEP קטן.

את תוצאות סימולציה זו ניתן להשוות למדידות הרעש בסיליקון.

סיכום

יעדי אימות רשת אספקות המתח של SOC הם:

לקבל כיסוי גבוה לכישלון תכנון

גילוי מוקדם של ליקויי תכנון וחולשות

אב טיפוס מוקדם ותכנון רשת האספקות

ניתוח סיבת הכישלון בכדי לשפר את הפרודוקטיביות עם אינטגרציה מלאה של השפעות כרטיס, אריזה ושבב.