איתן ריאחי, אלינה הנדסת אלקטרוניקה

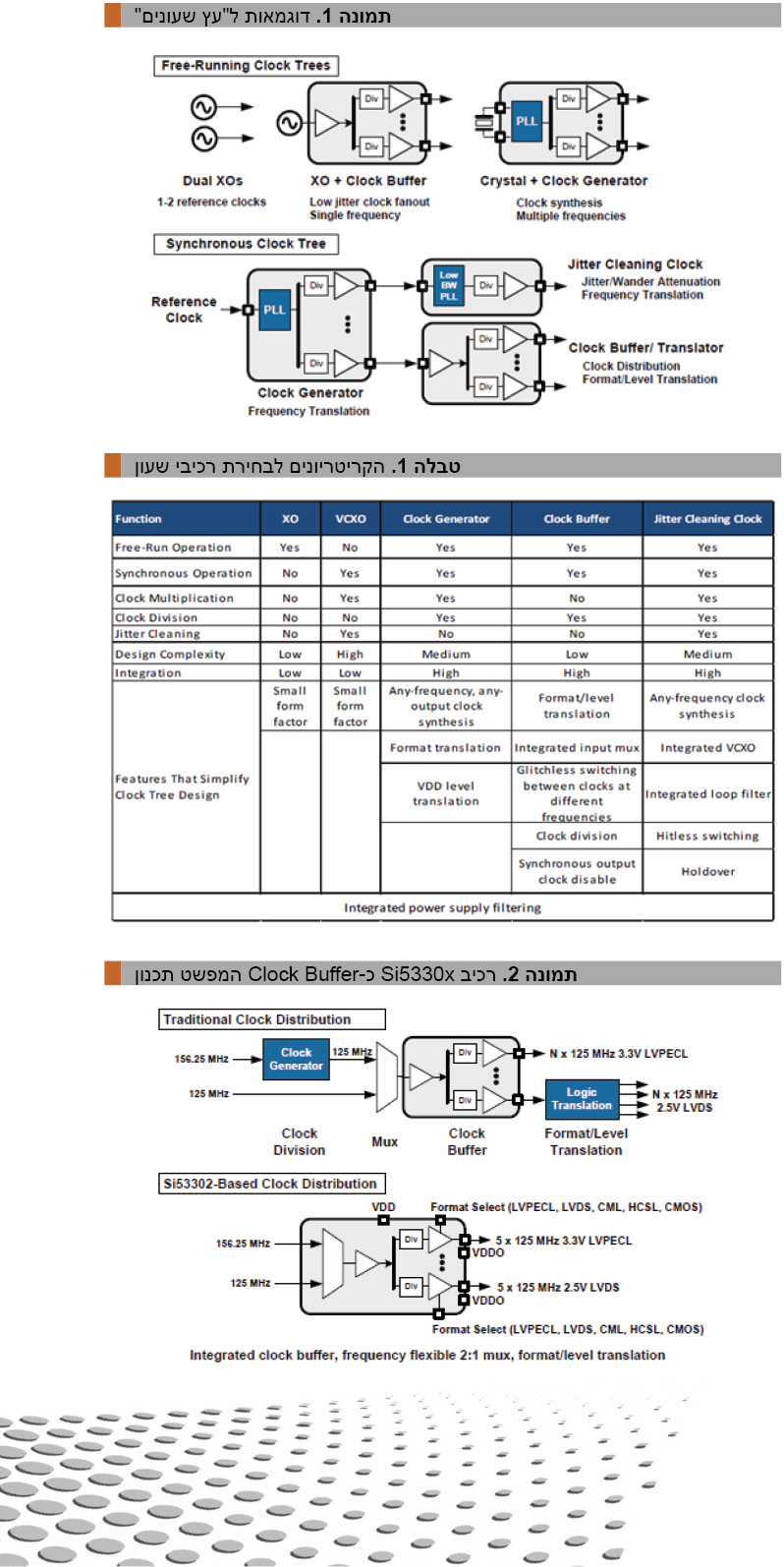

כנון החומרה ביישומים עתירי ביצועים הופך מורכב יותר ויותר, יישומים כגון: יישומי תקשורת אלחוטית, תשתיות, שרתים, שידור וידאו וציוד בדיקה ומדידה. שכן מערכות אלו משלבות יותר פונקציונליות ודורשות רמות הולכות וגדלות של ביצועים. מגמה זו מרחיבה את מורכבות "עץ השעונים" בכדי לספק את התזמונים הנחוצים למערכת. אסטרטגיית "מידה אחת תתאים לכולם" אינה חלה כאשר מדובר בתכנון "עץ שעונים". אופטימיזציה של "עץ השעונים" הינו דבר הכרחי בכדי לעמוד בדרישות הביצועים ובעלויות. וכן תלוי במספר גורמים: ארכיטקטורת המערכת, דרישות המעגלים המשולבים (IC), עיתוי (תדרים, תבניות אותות, וכו') ודרישות הריצוד (Jitter) של יישום האפליקציה.

תדר ייחוס – מתי עליי להשתמש בגביש ומתי בשעון ?

אחד משיקולי התכנון הראשונים הוא באפיון דרישות תדר הייחוס ובסוג השעונים שישמשו במעבדים, ברכיבי ה-FPGAs ,ASICs ,PHYs, במעבדי DSP וברכיבים שונים במערכת. גבישי קוורץ נמצאים בדרך כלל בשימוש כאשר לרכיב IC יש מתנד משולב ו-PLL לתזמון פנימי. גבישים הם רכיבים חסכוניים עם רמת רעש מופע (Phase-Noise) מצוין, והם זמינים באופן נרחב. הם גם יכולים להיות ממוקמים בסמיכות ל-IC, וזאת בכדי לפשט את העריכה. עם זאת, אחד מחסרונות הגבישים הוא שהתדר שלהם יכול להשתנות באופן משמעותי בשינוי טמפרטורה. ברוב יישומי SerDes מהירים בהם נדרשת יציבות ורגישות, מתנדי גביש (XOs) הינם מומלצים משום שהם מבטיחים יציבות (Stability) הדוקה יותר מאשר גבישים פסיביים.

מחוללי תדר וחוצצי תדר

(Clock Generators/Clock Buffers) נמצאים בדרך כלל בשימוש כאשר נדרשים מספר תדרי ייחוס. ביישומים מסוימים, רכיבי ה-FPGA/ASIC בעלי צורכי תזמון שונים לנתיבי הנתונים, נתיבי השליטה ולממשק בקר זיכרון ולכן דורשים תדרים רבים. מחולל השעון או החוצץ מועדף גם כאשר IC לא יכול להכיל קלט של גביש, וכאשר הרכיב חייב להיות מסונכרן לייחוס חיצוני, או כאשר נדרש תדר ייחוס גבוה שלא נוצר בקלות על ידי גביש.

"לרוץ חופשי" מול "עץ שעונים" מסונכרן

ברגע שמפרט השעונים הושלם ונבחרו הגבישים לחלק מהרכיבים, הצעד הבא הוא לבחור את התזמון לארכיטקטורה לשעונים שנותרו: "לרוץ חופשי" (free-running) או סינכרוני. עבור יישומים הדורשים שעון עצמאי אחד או יותר ללא כל דרישה מיוחדת לסנכרון או PLL, רכיבי XOs, מחוללי-תדר וחוצצי תדר הינן הבחירה המועדפת. המעבדים השונים, בקרי הזיכרון, ורכיבי SoCs ורכיבים היקפיים (למשל, ה-USB ומתגי-PCI Express) בדרך כלל משתמשים בשילוב של XOs, מחוללי-תדר וחוצצי תדר לעיתוי הפניה ביישומי "לרוץ חופשי", אסינכרוני. רכיבי XO עדיפים כאשר היישום דורש תדר ייחוס בודד (או לכל היותר שניים), ואילו מחוללי תדר וחוצצי-תדר מתאימים יותר ליישומים שדורשים מספר שעונים גדול יותר. מחוללי התדר יכולים לסנתז שעונים מרובים בתדרים שונים, אבל להקריב קצת ביצועי ריצוד בהשוואה לחוצצי שעון + עצי שעון XO. חוצצי שעון יכולים לשמש בשילוב עם תדר ייחוס XO להפיץ שעונים מרובים באותה התדירות ולספק ליישום ריצוד (Jitter) נמוך לעץ שעון מרובה פלט סנכרון השעונים והתדרים נמצא בשימוש ביישומים הדורשים סנכרון מתמשך ברמת רשת התקשורת, כגון ביישומים אופטיים – (Optical Transport Networking), יישומי SONET/SDH,Mobile Backhual, אטרנט, ושידור וידאו מסוג HD SDI.

יישומים אלה דורשים משדרים ומקלטים בכדי לפעול באותו תדר. סנכרון כל שעוני הייחוס SerDes בדיוק גבוה (לדוגמה, Stratum3 או GPS) מבטיח סנכרון בכל הצמתים. ביישומים אלה, שעונים המבוססים על PLL בעל רוחב סרט צר מספקים ריצוד (Jitter) וסינון (ניקוי ריצוד (Jitter) כדי להבטיח שהסנכרון ברמת הרשת נשמר. ביישומי כרטיס קו רשתות PLL, הפתרון המועדף לשעוני SerDes הינו מנחת ריצוד (Attenuator Jitter) מיוחד או PLL דיסקרטי עם מתנד VCOs. עבור ביצוע אופטימלי, הריצוד המונחת (Jitter Attenuator) צריך להיות ממוקם בסופו של עץ השעון, המפעיל את ה-SerDes באופן ישיר. מחוללי תדר וחוצצי-תדר יכולים לשמש כדי לספק מערכות ייחוס אחרות.

Clock Jitter

ריצוד השעון הינו קריטי עבור רכיבי התזמון כאשר חריגה בריצוד שעון יכולה לפגוע בביצועי המערכת. קיימים שלושה סוגים נפוצים של ריצוד שעון, ובהתאם ליישום, סוג אחד של ריצוד יהיה חשוב יותר ממשנהו.

ריצוד מחזור למחזור (Cycle to Cycle jitter) – מודד את השינוי המרבי בין כל שני מחזורי שעון סמוכים, כאשר נמדדים בדרך כלל מעל 1,000 מחזורי שעון.

ריצוד תקופתי – (Period Jitter) – התקופה היא הסטייה המרבית בתקופת השעון ביחס לתקופה האידיאלית במספר רב של מחזורים (10,000 מחזורי שעון אופייני). שני הסוגים קרי, ריצוד מחזור למחזור וריצוד תקופתי שימושיים בחישוב מבנה "עץ השעונים" כך שבמערכות דיגיטליות יהיה מרווח מספק (Margin) לגורמי האיכות של רכיבי ה-CPU וה-SoC.

ריצוד "שלב" (Phase Jitter) בגורמי האיכות ליישומי SerDes במהירות גבוהה. זה יחס של אות לרעש המחושב על ידי שילוב של רעש מופע השעון יחיד על פני מגוון רחב של תדרים. ריצוד "שלב" קריטי במיוחד ברכיבי FPGA ובמערכות SerDes מהירות גבוהה, כאשר ריצוד מוגזם יכול להוריד את שיעור השגיאה.

במהלך תכנון "עץ השעונים" ובחירת רכיבים, חשוב להעריך מכשירים המבוססים על ביצועי ריצוד מקסימלית. מפרט ריצוד טיפוסי אינו מבטיח את ביצועי מכשיר תחת כל התנאים, ובכלל זה שינוי בתהליך, במתח, בטמפרטורה ושינוי בתדר. הריצוד המקסימלי (Jitter) מספק מפרט מקיף יותר של גורמים נוספים אלה.

בנוסף לכך, יש להתייחס בעיון רב לתנאי הבדיקות של רכיבי התזמון במפרט הניתן. ביצועי ריצוד שעון משתנים על פני מגוון רחב של התנאים, כולל תצורה, תדירות הפעלה מכשיר, תבנית האות, קצב שינוי שעון קלט, מקור המתח ורעש מקור המתח. יש לחפש רכיבים המציינים באופן מלא תנאי בדיקת הריצוד שכן הם מבטיחים פעולה על פני טווח הפעלה רחב יותר.

בחירת שעונים ורכיבי אוסילציה

ברגע שארכיטקטורת "עץ השעונים" נקבעה, השלב הבא הוא בחירת הרכיבים. טבלה מס' 1 מסכמת את הקריטריונים לבחירת רכיבי שעון ומתנד עבור שני סוגי עצי השעון: "לרוץ חופשיים" ו"סינכרוני". חפש תכונות המפשטות את תכנון "עץ שעונים" על מנת להקטין את עלות ה-BOM ומורכבותו.

חברת Silicon-Labs מציעה מבחר רחב של מחוללי תדר שעון גמישים, חוצצי- תדר, שעוני ניקוי ריצוד (Jitter)

ו-VCXOs/XO, ובכך מספקת ביצועים גבוהים ביותר בתעשייה ופתרונות עץ שעונים משולבים.

חברת Silicon-Labs משקיעה במחקר ופיתוח כדי לעזור ללקוחותינו לבדל בשוק עם צריכת חשמל נמוכה חדשני, גודל קטן, פתרונות אותות מעורבים אינטנסיביים אנלוגיים. תיק הפטנטים הנרחב חברת Silicon-Labs הוא עדות לגישה הייחודית שלנו וצוות הנדסה ברמה עולמית.

פרטים נוספים באתר החברה.