היום מוצרים רבים מתוכננים לצריכת הספק נמוכה ועבודה מסוללה לזמן רב, כאשר רוב המוצרים מכילים מעבד שתוכנן לצריכת הספק נמוכה. כשנבחן מעבד זה נמצא כי מעבד CMOS צורך הספק בשני דרכים: הספק סטטי וזרמי זליגה, והספק דינמי בזמן עבודה. ההספק הדינמי נצרך כאשר השער הלוגי מחליף מצב, וצריכה ההספק הדינמי נקבעת בעיקר ע"י הפרש המתחים בין המצבים ומהירות החלפתם. קיימים היום פתרונות די סטנדרטיים להורדת הספק ע"י מיתוג חלקים שונים בשעונים שונים ומשתנים, או ע"י אזורי הספקה שונים הניתנים לכיבוי. במאמר זה נעסוק במתח הפעולה של הרכיב. וכפי שרואים בתמונה 1 האנרגיה הנצרכת היא חזקה ישירה של המתח, כלומר הורדת מתח הפעלה היא המפתח להורדת הספק במערכות עתידיות.

עבודה במתח תת-סף

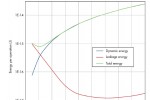

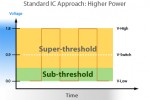

Ambiq Micro לקחה על עצמה את אתגר הורדת המתח ע"י הפעלת הרכיב במתח תת-סף המיתוג (ראה תמונה 2 ו-3), והחיסכון שהושג הוא אדיר. מעגל CMOS סטנדרטי וזול עובד ב-1.8V, אבל הפעלתו ב-0.5V ישפר את צריכת ההספק פי 13. ועל ידי הפעלת טכניקה מתקדמת יותר ניתן להפעיל את המעגל ב-0.3V כדי להשיג עד פי 36 שיפור בצריכת ההספק.

הפעלה במתח תת-סף היא לא טכניקה חדשה, שעונים שוויצריים ותגי RFID משתמשים בה מ-1970 ו-Ambiq Micro עצמה התחילה ב-2004 כמחקר באוניברסיטת מישיגן. אז למה לא פגשתם עד היום מעבדים העובדים במתח תת-סף? התשובה היא התהליכים המורכבים של תכנון ויצור רכיבי CMOS, ולכן עד לאחרונה טכנולוגיה תת-סף שימשה רק רכיבים שהכילו עד עשרות טרנזיסטורים בודדים. נבחן את מורכבות ההמרה של תהליך COMS לתמיכה במתח תת-סף.

מודלים חלקים של טרנזיסטורים

טרנזיסטורים תוכננו לעבוד במתחי סף סטנדרטים, ולכן המודלים התכנוניים מאוד מדויקים עבור מתחים אלו, אבל אינם מדויקים עבור עבודה במתח תת-סף שאינו נחשב אזור עבודה.

מיתוג ורעש

מיתוג במתח תת-סף הוא עדין ודורש רגישות ודיוק. כאשר משווים מיתוג רגיל למיתוג בתת-סף אנחנו רואים הפרש של פי 1000 ברגישות לזרם הנדרשת, אתגר לא פשוט, ראה תמונה 4. עכשיו תוסיפו לרגישות הנדרשת רעש…

יצור ושונות ביצור

יצור פרוסות סילקון משתמש בבחינת פרוסות קצה (Corner Lots) כדי להבטיח איכות ואחידות – באזור התת-סף השונות בין פרוסות קצה לרגישות זרם יכולה להגיע אף לפי 100. עובדה זו מקשה מאוד על תכנון רכיב העובד בנקודת סף. תוסיפו משתני הפעלה של הרכיב כמו טמפרטורת הסביבה (ראה תמונה 5) ותקבלו אתגר כפול לתכנן רכיב תת-סף.

בחינות איכות

תהליכי בקרת יצור CMOS תוכננו לבחינה ואפיון של רכיבים סטנדרטים, וכדי לבחון רכיב תת סף היה צורך לפתח תהליך חדש היכול לבחון זרמים של ננו ופיקו אמפר במקום מיקרו אמפרים.

Sub-threshold Power Optimized Technology (SPOT)

תוך הבנת האתגרים הללו ומחקר אינטנסיבי לאורך שנים הצליחה Ambiq Micro לפתח טכנולוגיה פורצת דרך לרכיבים העובדים במתח תת-סף ומיוצרים בטכנולוגית סיליקון סטנדרטית וזולה. טכנולוגיה זו נקראת – threshold Power Optimized Technology

(). ומאפשרת יצור סדיר של רכיבים דלי הספק.

כדי להתמודד עם האתגר של פיתוח ויצור מסחרי של רכיבי תת-סף השתמשה Ambiq Micro בכמה שיטות עיקריות: מיטות בדיקה ייחודיות ורגישות במיוחד המרחיבות את יכולות הבדיקה הסטנדרטיות ביצור רכיבי CMOS. שילוב של מעגלי בדיקה ופיצוי מוכללים ברכיבים עצמם להשלמת כיסוי של הבדיקות הנוספות הנדרשות ופיצוי על ביצועי קצה בהתאם. וכן דיוק ופירוט רב יותר של אפיון פרוסות הסיליקון כדי להבטיח איכות וגמישות יצור. כל אלו נוספו על התהליכים הסטנדרטיים של יצור ובדיקה של רכיבי CMOS הכוללים בחינה של פרוסות קצה וחשיפתם לתנאי פעולה קיצונים (טמפ') לאורך זמן ובדיקות ESD. התבססות על תהליכים סטנדרטיים תאפשר לטכנולוגיה SPOT להוביל את עולם רכיבי ההספק הנמוך גם בשימוש בגאומטריות יצור סיליקון קטנות יותר ויותר כשאלה יהפכו לכלכליים.

גישה חדשנית זו לתכנון רכיבי SPOT החל מפיתוח טרנזיסטור ייעודי, דרך פיתוח תהליכי יצור ובדיקה ייעודים הובילו את Ambiq Micro ליצור של רכיבים דלי הספק הדומים כמעט בכל לרכיבים סטנדרטיים. כאשר הרכיבים הראשונים שיוצרו בטכנולוגיה SPOT הם שעוני זמן אמת (), AM08xx ו-AM18xx, רכיבים אילו תוכננו כדי לנהל את ההספק במעגל אלקטרוני ומכילים זיכרון עם זרם זליגה אפסי של עד 256 ביטים. בטמפרטורה של 30 מעלות ומתח הפעלה של 3 וולט הם צורכים רק 14nA הרבה פחות מכל רכיב RTC בשוק. RTCs אלו כבר ביצור שוטף ומוטמעים במוצרים רבים.

השלב הבא יהיה בשבועות הבאים כאשר החברה תכריז על מעבדים 32 ביט בטכנולוגית SPOT, שיקבעו רף חדש למעבדים דלי הספק.

- תמונה 1

- תמונה 2

- תמונה 3

- תמונה 4

- תמונה 5